Descrevemos neste artigo um excelente transmissor de FM e VHF sintetizado (PLL). O artigo é de nosso colaborador Nelson Sedenho Junior, contendo também o circuito multiplex para transmissões estéreo. A grande vantagem deste circuito está na estabilidade de frequência dada sua síntese por um circuito PLL.

Quando tentamos elaborar um projeto de um transmissor de rádio para altas frequências, modulado em frequência, como é o caso de VHF, nos deparamos com alguns problemas, como a eventual necessidade de um único oscilador a quartzo, seguido por multiplicadores, para que se alcance a frequência desejável, além de um razoável desvio naquela que fora gerada pelo cristal, que a produz de maneira muito estreita quanto à esta característica, justamente devido à sua alta estabilidade e precisão de oscilação, que o definem.

Isto, para comunicações em 2 metros, não chega a ser um problema, já que o desvio necessário a que se consigam 100% de modulação, é de apenas 5 kHz; mas, mesmo assim, se utilizamos um único oscilador, a cristal de quartzo cuja frequência seja um divisor exato daquela a ser emitida (como, por exemplo, um de 14,5 MHz, que, multiplicado por 10 pelos estágios amplificadores de RF, proporcione a frequência final desejada, de 145 MHz), “seguido” por multiplicadores de frequência, ocorrem dois inconvenientes: primeiro: o equipamento necessita, entre um estágio e outro, de filtros corta-faixa “notch” elípticos (como os LC, de Cauer) de ótimo fator Q, para que as frequências harmônicas intermediárias (e a própria fundamental, gerada pelo oscilador) não cheguem à antena, sob pena de se gerarem enormes interferências no espectro eletromagnético; segundo: como a frequência gerada deve ser multiplicada, até que se alcance a desejada para a emissão, os amplificadores de RF que o fazem proporcionam amplitudes de saída muito inferiores àquela que produziriam, caso já ressonassem na frequência fundamental do oscilador, apenas intensificando o sinal por ele gerado. Além disso, um modulador de rádio “singelo” feito deste modo também “engessa” o radioamador a utilizar uma única frequência emitida, múltipla da gerada pelo cristal de quartzo (ou apenas mais algumas, no caso de se utilizar mais de um cristal, com chave seletora conectada ao oscilador), sem se mencionar a forte distorção do áudio emitido, posto que o cristal de quartzo, por definição, não admite variações de frequência grandes, em relação à sua de ressonância (isto quando o varicap, capacitor e bobina em série consigo, não o instabilizam, ou o impeçam de oscilar!).

Porém, para a nossa “sorte”, a tecnologia evoluiu nas últimas décadas e, com o advento da eletrônica digital, as telecomunicações tiveram um enorme salto de qualidade, no que diz respeito à geração direta de sinais altos de VHF, µHF, ou mesmo SHF, com precisão e estabilidade de quartzo, e possibilidade de, em um único equipamento transmissor e/ou receptor de RF, gerar-se uma enorme gama de frequências, com um número relativamente pequeno de componentes. E uma destas “maravilhas” tecnológicas foi a invenção do sistema de “elo” (ou “malha”) “amarrada por fase”, ou PLL (“phase locked loop”), em Inglês; e o projeto que elaborei utiliza esta tecnologia, muito embora, atualmente, existam circuitos mais sofisticados, à base de circuitos integrados DSP, microcontroladores PIC, lógicas EPROM, ou mesmo os dedicados da Motorola, como o MC145151 ou 145152, por exemplo, porém são mais onerosos ao montador. Mas, este que ora apresento, além de ser simples e barato, possui ótimas características, como:

- A possibilidade de se gerarem, diretamente, várias frequências de VHF, até 120 MHz (frequência máxima com a qual o “prescaler” pode “trabalhar”), apenas alterando-se o fator “n” do divisor lógico programável, em BCD (e, se necessário, também alterando-se o valor de L e/ou C do VCO, caso não consiga ser sincronizado pelo PLL);

- Baixíssimo custo, devido ao uso de circuitos integrados comuns e fáceis de se achar no comércio, ou pela internet;

- Possuir um oscilador livre controlado por tensão (“VCO”, em Inglês), de alta linearidade de modulação e baixíssimo ruído de portadora;

- A não necessidade de se fazerem quaisquer programações externas, via software e microcromputador (como ocorreria com projetos com PIC, DSP e/ou EPROM);

- Utilizar um ótimo filtro passa-baixas entre a saída do comparador (ou detector) de fase e a entrada do VCO, que o faz receber, em seus diodos varactores, um CAF (ou “AFC”, em Inglês) limpo, muito próximo a zero Hz, sem apitos, roncos, instabilidades ou ruídos que, indevidamente, o modulassem em frequência; tal AFC só varia (obviamente) em amplitude de tensão contínua, de modo proporcional ao erro de frequência do VCO, para corrigi-lo e/ou força-lo a produzir as corretas frequência e fase do sinal de RF, o que caracteriza e define os sistemas PLL;

- Rápida sincronização, seja por (indesejáveis) variações de temperatura, umidade, tensão, envelhecimento do oscilador, etc., que o levassem (o VCO) à deriva, seja por alteração (proposital) do fator “n” do divisor lógico programável, para a necessária alteração da frequência da portadora a ser emitida;

- Possibilidade de ser utilizado na faixa comercial de FM, devido ao fato de se conseguirem, facilmente, 75 kHz de desvio de frequência do sinal gerado, se necessário (e, é claro, também 5 kHz, caso seja utilizado, por exemplo, em VHF 2 metros), com alta linearidade e baixíssima distorção, devido ao óbvio fato de o VCO ser um oscilador livre LC, e modulado diretamente pelo sinal de áudio;

- Altíssima precisão e estabilidade da portadora gerada (um protótipo – dentre três - que montei para um amigo, que o utiliza como “rádio comunitária” de alguns microwatt, com alcance restrito à sua residência, amigo este que me informou que o programou para operar em 96,5 MHz, e o ligou em um frequencímetro, o qual dera, em seu display, a leitura de numeração de 96,50000 MHz, sem variação alguma, em nenhum dos dígitos), sem os comuns “ripples” advindos de filtros passa-baixa ineficientes, existentes em transmissores PLL ruins (no caso em epígrafe, caso fosse um PLL ruim, os dígitos variariam, por exemplo, entre 96,49999 e 96,50001 MHz; é claro que os rádios digitais, no “scan”, os sintonizariam, mas é um enorme inconveniente técnico, até por questões de normas internacionais de telecomunicações). O protótipo dele (assim como os outros dois que, também, eu montei) se mostrou altamente estável e preciso, daí isto ter sido mostrado pelo display do frequencímetro.

UM POUCO DE HISTÓRIA

Vendo livros de Eletrônica da década de 60, verifiquei um artigo, no mínimo, interessante, acerca de transmissores de FM para radiodifusão: era um projeto (hipotético), valvulado, que funcionava da seguinte forma: eram utilizados dois osciladores, um livre com uma válvula de reatância (varactora) conectada ao seu circuito tanque LC, e um outro, também valvulado, a cristal de quartzo; o LC recebia o áudio para ser modulado em FM, e tinha o seu sinal de RF amplificado por outras válvulas, após a sua regeneradora; o oscilador a quartzo, por sua vez, tinha o seu sinal acoplado a um circuito de batimento que o autor afirmava chamar-se “Fost-Seller”, o qual também recebia o sinal do oscilador livre, já amplificado. Do batimento das frequências geradas por ambos, acoplado a um transformador de FI, surgia, no secundário deste último, uma tensão alternada, proporcional à diferença de fase e frequência dos sinais advindos dos dois osciladores; esta tensão era retificada e filtrada, por um integrador RC, para, então, ser acoplada à grade da válvula de reatância que estava conectada ao circuito LC da osciladora. Segundo o autor, esta tensão contínua, proporcional ao erro de frequência (que, obviamente, só poderia vir do oscilador livre, já que o a quartzo é altamente estável e preciso) fazia variar a capacitância grade-anodo da válvula de reatância, corrigindo-o, deste modo. Não seria, então, este um transmissor PLL analógico? O princípio de funcionamento comprovava que sim, até pelo fato de o autor afirmar que, àquela época, era o que possibilitava a existência de um transmissor de FM que, ao mesmo tempo, propiciasse estabilidade de quartzo e 75 kHz de desvio de modulação, ou seja, destinado à radiodifusão comercial.

VANTAGENS QUE UM EQUIPAMENTO PLL PROPICIA

Pelas linhas acima, é fácil abstrair que transmissores (e/ou receptores) de RF que utilizam um PLL na síntese do(s) sinal(is) gerado(s), apresentam, no mínimo, as seguintes características altamente interessantes:

- Seus circuitos geram, pelo VCO, diretamente a frequência fundamental a ser utilizada, sem a necessidade de circuitos multiplicadores;

- Como, por definição, o VCO (oscilador controlado por tensão) é forçado a produzir um sinal que fique em fase com o gerado pelo oscilador de referência, a estabilidade e precisão do sinal produzido pelo primeiro são as mesmas do produzido pelo segundo; assim, como sempre é utilizado um oscilador a quartzo (cuja variação é de poucas partes por milhão – ppm -em relação à sua frequência de ressonância, ou seja, de alguns Hz em relação aos vários MHz com que o cristral vibra – e isto, sem que o alojemos em uma câmara térmica!), como referência, o VCO passa a ter a sua mesma estabilidade e precisão de frequência;

- Como a frequência do oscilador a quartzo normalmente é também dividida digitalmente, antes de ser acoplada ao detector de fase, o ínfimo erro de frequência do cristal (de alguns Hz, como dito acima, ou mesmo décimos de Hz) também é dividido; assim, é fácil concluir que um transmissor PLL tem precisão de frequência ainda maior do que a (já enorme) obtida por um que utilize, apenas, um simples oscilador a cristal de quartzo, posto que o VCO, como dito acima, fica em fase com o sinal de referência (no caso, a altamente estável e fixa frequência gerada pelo cristal de quartzo, e com o seu desprezível erro, que, ainda por cima, é dividido digitalmente!);

- Pelo fato de o oscilador controlado por tensão (VCO) ser livre, LC, seu “range” de produção de frequências diferentes é enorme. Em um PLL, isto é aproveitado pois, por exemplo, se em um transmissor de FM, devemos gerar frequências entre 87,5 e 108,0 MHz, tal espectro é, facilmente, obtido com um simples oscilador LC. E, se um oscilador livre LC consegue tal “varredura” de mais de 20 MHz, é claro que um desvio bem menor, de até 75 ou 100 kHz, para modulação FM, ele também permite. Deste modo, um transmissor como o do projeto abaixo consegue ser programado, digitalmente, a partir de um só cristal de quartzo como referência, para gerar qualquer frequência dentro dos limites do VCO, só sendo necessário, em alguns casos, aumentar ou diminuir a sua constante LC, para que o sistema sincronize, travando-o em fase. Além disso, qualquer das frequências geradas (uma por vez, dependente da programação BCD do divisor digital por “n”) terá uma modulação FM de alta qualidade, extremamente linear, já que as variações de amplitude do sinal modulante são aplicadas, diretamente, aos diodos varicap (varactores) constituintes do circuito LC;

- Pelo dito nas últimas linhas acima, outra vantagem do PLL é, justamente, a possibilidade de se fazer a modulação FM direta, acoplada já à geração da portadora, no circuito de reatância do VCO, através de seus diodos varicap, polarizados reversamente pelo AFC (cuja tensão é proporcional à frequência a ser gerada, e também ao seu erro, caso o VCO tenda a “fugir” da fase correta), e pelo próprio sinal modulante (no caso, audiofrequências).

Diante do acima exposto, é fácil entender porque, atualmente, todas as emissoras comerciais de rádio e televisão, os sistemas de telefonia celular, radiocomunicação, entre muitos outros, utilizam os “phase locked loop” em seus equipamentos, devido à alta confiabilidade que os seus circuitos proporcionam, para fins profissionais.

O PROJETO

1- VCO E “BUFFER”

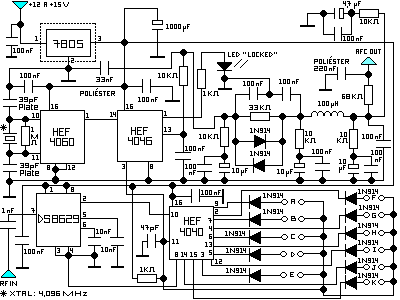

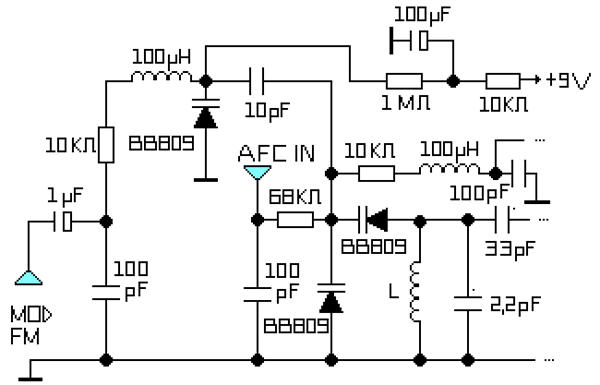

Como mostram os dois esquemas elétricos, o modulador de FM/VHF se constitui pelo VCO e “buffer” (figura 1), e pelo sintetizador digital de frequências (figura 2), ambos constituintes do sistema de elo amarrado por fase, PLL, em questão.

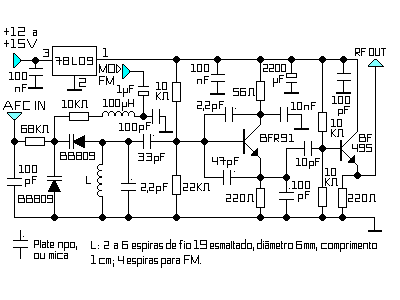

O VCO utiliza um oscilador Clapp com um transistor de alta frequência (fT de 6 GHz), um BFR90 ou 91, em emissor comum; apesar de esta configuração em muito amplificar as capacitâncias parasíticas internas às junções PN do referido semicondutor, como ele é projetado para frequências muito maiores do que as de VHF a que se destina o projeto, pelo fato de ser um transistor de tecnologia “epitaxial planar” de alta frequência de transição, fabricado para gerar ou amplificar sinais de microondas, sua utilização no projeto é nada crítica. Na falta dele, pode até ser utilizado um transistor de VHF, como um BF494 ou 495, por exemplo, porém, neste caso, haverá um maior ruído branco na portadora, devido ao fato de estar polarizado em emissor comum, o que o aproxima, muito, de sua fT (de 250 MHz), no projeto em questão.

O circuito tanque LC é acoplado à base deste transistor, o qual o realimenta e amplifica, produzindo, deste modo, o sinal de RF. Como o projeto se destina a produzir altos sinais de VHF, recomenda-se que seja feito em partes, sendo, portanto, interessante começá-lo por este oscilador. Assim, desconectado que, inicialmente, estará do sintetizador, é necessário que, por ora (quando dos testes do oscilador e “buffer”), não se soldem os diodos varicap, ou varactores, no caso os BB809 (ou BB405, BB109, etc.) pois, caso contrário, como estarão desprovidos inicialmente do AFC que viria do sintetizador, causariam alta instabilidade sobre o oscilador, além de fortes roncos de 60 Hz na modulação, já que, sem tensão contínua polarizando-os reversamente, ficam vulneráveis a sinais elétricos externos, além de, nestas condições, se comportarem como capacitores “aleatórios” de alguns pF, o que justifica a instabilidade de frequência que causariam sobre o circuito ressonante LC do VCO.

Deste modo, enquanto não estabilizado pelo PLL, o VCO deve, inicialmente, apenas gerar uma portadora de certa estabilidade, e de sinal limpo, livre de roncos e/ou ruídos brancos. Para tal, é imprescindível que seja montado em “gaiola de Farad”, com blindagens metálicas retangulares, que podem ser feitas com pedaços de latas de leite em pó, convenientemente recortadas de acordo com as dimensões da placa de circuito impresso, soldadas ao redor desta (uma vez que, no seu “layout”, a linha do “zero volt” da terra deverá contorná-la, devendo, para tal, ser desenhada, com trilhas grossas, nas suas quatro laterais). Se ela for de fibra de vidro, será a melhor opção; no entanto, como o aparelho é altamente confiável e estável, sua montagem em placa de fenolite também é possível e não o impedirá de funcionar adequadamente.

Pelo fato de o PLL compensar quaisquer desvios de frequência e fase oriundos de instabilidades do VCO (por variação de temperatura, tensão, umidade relativa do ar, capacitâncias da caixa metálica em que o aparelho for alojado, etc.), quaisquer capacitores de boa qualidade podem ser empregados no circuito LC ressonante, como os cerâmicos, por exemplo. No entanto, se possível, a utilização dos que possuem compensação negativa de temperatura (“plate NPO”, ou mica prateada) é recomendável, devido à sua maior estabilidade e precisão de capacitância, frente a variações de temperatura e umidade do ambiente (que o AFC do PLL compensará), e ao menor ruído branco que proporcionam à portadora. Assim, os capacitores plate ou de mica são melhores, para os de capacitância de valor picofarádico do VCO; dentre eles, vê-se um de 2,2 pF, entre a base e coletor do transistor oscilador: a sua função é “cancelar a fase” de 180º existente entre estes eletrodos internos do semicondutor, os quais são, respectivamente, a sua entrada e uma de suas saídas de sinal; deste modo, acoplado entre a base e o coletor, o referido capacitor em muito reduz o já baixo ruído branco produzido pelo transistor. Os demais, de nanofarads, podem ser cerâmicos comuns. Quanto ao capacitor eletrolítico de 2200 µF por 10 ou 16 V, que filtra eventuais ondulações de VCC (“ripple”) que não tenham sido eliminadas pelo regulador de 9V (que, como todo 78XX, as rejeitam em 60 dB, diminuindo a sua amplitude em 1000 vezes, ou seja, para cada 1 V de ondulação do gerador não estabilizado, apenas 1 mV alcança o circuito alimentado pelo CI regulador), recomenda-se que não seja soldado rente à placa de circuito impresso; nos protótipos que montei, percebi que, devido à sua indutância parasita (embora desacoplada pelos capacitores cerâmicos de 100 nF e de 100 pF – este último destinado a evitar que qualquer sinal de RF do oscilador chegue ao +B, que o alimenta), o eletrolítico em questão pode produzir um ruído indesejável, semelhante a um apito, devido a possíveis realimentações com o regulador 7809, e com o próprio oscilador. Também notei que a tal indutância do eletrolítico pode induzir ruído branco, na portadora gerada pelo VCO; desde modo, solde-o de modo a que seus lides tenham cerca de 1 cm de altura, em relação à base da placa do oscilador; também é recomendável que ele fique cerca de 1,5 cm distante, ou um pouco mais, dos outros componentes do VCO. Outra “dica” é, caso o VCO tenha furos na placa para fixação dos componentes (que ficariam, deste modo, na sua parte isolada, sendo a cobreada responsável apenas pelas soldas dos terminais deles), que o transistor oscilador seja soldado na parte cobreada da placa, pois isto, em muito, aumenta a estabilidade do VCO (ainda sem receber o AFC do PLL) e diminui consideravelmente o ruído da portadora; de todo modo, se a montagem for feita diretamente sobre a superfície cobreada da placa (em “SMD”, portanto), seu comportamento é melhor, devido ao fato de trabalhar com sinais de alta frequência. Notará o leitor que, seja como oscilador livre, seja como estabilizado pelo PLL, o VCO , se convenientemente montado, produzirá uma portadora limpa, sem ruídos, comparável (e, em alguns casos, até superior) àquela gerada por emissoras comerciais de FM, quando as sintonizamos sem modulação e aumentamos o controle de volume de nossos “receivers”. Um dos motivos pelos quais isto ocorre é o fato de o BFR90 (ou 91), por ser projetado para SHF (fT de 6 GHz), trabalhar “com folga” para gerar sinais com frequência 50 ou mesmo 60 (se o PLL for gerar frequências próximas a 100 MHz) vezes inferiores à sua de transição.

Quando VCO for inicialmente testado (e mesmo depois, em plena operação, com o PLL), alimente-o com uma fonte de 12 a 15V, bem filtrada, estabilizada e montada em caixa metálica conectada ao seu terminal de terra, para que se evitem grandes derivas da frequência gerada e, sobretudo, roncos e zumbidos. É claro que, com o PLL, não haverá estes desvios de frequência oriundos do “ripple” de fontes ruins, mas certamente haverá roncos, na transmissão.Assim, caso o transmissor não seja alimentado por acumuladores de carro ou moto, que são as melhores fontes de corrente contínua para tal (devido às altas amperagens neles disponíveis e, sobretudo, à total ausência de ruídos, por serem geradores químicos), é imprescindível que a fonte de alimentação seja, como dito acima, bem filtrada, estabilizada e montada em caixa metálica, aterrada. Como o LC utilizado é fixo, caso não se consiga sintonizar a oscilação livre do VCO em um rádio receptor (como um de FM, caso seja montado para operar nesta faixa), pode-se apertar ou alongar, cuidosamente, a bobina osciladora, até que se obtenha a recepção do sinal em uma frequência livre de emissoras, no rádio. Se o montador dispuser de um frequencímetro ou osciloscópio, pode utilizá-lo(s), conectando-o(s) à saída do “buffer”: conecte, para tal, um capacitor entre 10 e 100 pF, no emissor do BF495 ou 494. A tela do osciloscópio mostrará a existência de um sinal senoidal, porém de período instável (principalmente se os capacitores e/ou a bobina do VCO forem tocados, ou receberem calor, umidade etc.), devido ao fato de, naquele momento, não estar amarrado ao PLL. No caso de se utilizar um frequencímetro, o sinal monitorado terá, indefinidamente, uma grande alteração nos dígitos do display, principalmente nas “casas” após a vírgula ou ponto (tal não ocorrerá quando o PLL estiver ligado ao VCO: a frequência, neste caso, surgirá, no display, com todos os dígitos “parados”, sem variação alguma, como mencionarei parágrafos abaixo). Deste modo, fica evidente que, por melhor que seja, qualquer oscilador livre, LC ou RC, gera um sinal de tensão alternada de frequência aleatória, sem estabilidade e precisão alguma, daí a necessidade do PLL. Ainda com relação à bobina osciladora, ela terá núcleo de ar, e se constituirá de 2 a 6 espiras de fio 19 esmaltado (conforme a gama de frequências de VHF que se pretenda gerar, com o PLL), com diâmetro interno de 6 mm, e comprimento de 1 cm; assim como o capacitor eletrolítico de 2200 µF, é interessante que esta bobina também fique um pouco afastada da base da placa, com os lides tendo cerca de 7 mm de altura, para evitar a produção de ruído branco, na portadora. Caso o equipamento seja destinado à faixa comercial de FM, entre 87,5 e 108 MHz, tal bobina terá 4 espiras. Caso o montador queira, pode confeccioná-la sobre um núcleo ajustável de ferrite, para que se altere a sua indutância, para mais ou para menos, de modo a que o PLL force o VCO a produzir a frequência desejada, sincronizando-o; neste caso, é interessante que a bobina variável tenha blindagem externa (semelhante às “canecas” das de FI de receptores de rádio), soldada à terra do oscilador.

Como vemos no esquema, o coletor do BFR91 é desacoplado, via capacitor cerâmico (ou plate, se possível), de 10 nF: tal conexão à terra diminui, em muito, o já baixo ruído branco produzido pelo oscilador; no entanto, possui o inconveniente de atenuar, consideravelmente, a amplitude de RF do sinal gerado (motivo pelo qual ele é retirado do emissor do referido transistor). Deste modo, após ser retirado do transistor isolador aperiódico (“buffer”) do VCO, o BF495, se for intensificado para, após, ser acoplado à antena de transmissão, as etapas amplificadoras de RF devem ser de alto ganho e/ou em um número alto (de, no mínimo, 3 ou 4 circuitos amplificadores), para que se obtenha potência suficiente para um longo alcance, ou para excitação de posterior elemento amplificador de alta potência, transistorizado, valvulado, ou constituído por circuitos integrados módulos projetados para VHF. Assim, para as primeiras etapas, deverá haver um ganho razoável de amplitude de RF, para que o pequeno sinal gerado por este modulador seja capaz de acender uma pequena lâmpada incandescente, ou excitar um wattímetro ou medidor de ROE, acoplado à uma carga de 50 ?. Ainda com relação ao “buffer”, para o devido casamento de impedâncias com a etapa amplificadora de RF à qual ele for conectado, optou-se pela configuração de coletor comum (seguidor de emissor), com o coletor do BF495 ligado diretamente ao +B da fonte, e o emissor à saída do sinal de VHF produzido pelo circuito, que também alimentará a entrada do circuito integrado “prescaler” do PLL. Nota: como são montados em placas separadas (devidamente blindadas por “gaiolas de Farad”), a conexão entre a saída de RF do VCO/“buffer” e a entrada do PLL (CI DS8629, “prescaler”), e a outra, existente entre a saída do filtro passa-baixas do detector de fase do PLL e a entrada do VCO (diodos varicap BB809, ou BB405, BA102, BB109 etc., para VHF ou µHF), devem ser feitas por cabos blindados de boa qualidade, com as malhas devidamente aterradas¸ a fim de que se evitem instabilidades (principalmente as que impediriam o PLL de “lockar”, no momento da sincronização), ruídos, roncos, zumbidos, etc. Aliás, as montagens do VCO/ “buffer” e do sintetizador PLL foram feitas deste modo, em duas placas de circuito impresso distintas e devidamente blindadas, propositalmente, para que não houvesse apitos e/ou ruídos de “jitter” dos divisores digitais CMOS do sintetizador sobre o VCO e, reciprocamente, para que a RF gerada por este, não interferisse nas sensíveis portas lógicas destes integrados, o que os levaria a níveis lógicos erráticos e/ou “thresholds”, que impediriam o PLL de travar.

Quanto ao regulador de voltagem que alimenta esta placa do transmissor, só uma ressalva: como o VCO e do “buffer”, juntos, drenam cerca de 20 mA da fonte de alimentação, achei um desperdício o uso de um LM7809, que pode fornecer até 1 A, à carga; portanto, nos protótipos, utilizei o 78L09, de invólucro e dimensões menores, até porque trabalha sem aquecimento algum, neste projeto. Porém, a sua pinagem é inversa em relação a daquele: enquanto o LM7809 recebe o +B da tensão não regulada pelo pino 1, e a fornece estabilizada pelo 3, o pequeno 78L09 faz justamente o inverso (a sua entrada é o pino 3, e sua saída, o pino 1). Assim, o mesmo “layout” da placa pode ser utilizado para receber qualquer um destes CIs estabilizadores de tensão, porém deve-se atentar para o fato de que um é “espelhado” em relação ao outro, quando de seu encaixe e solda; apenas o pino 2, conectado à terra, é que lhes é idêntico, quanto à ligação ao circuito.

Como demonstra o esquema elétrico, não há capacitor de isolamento de tensão contínua, na saída de RF do “buffer”; tal se deve ao fato de, na entrada do sintetizador PLL (pino 7 do “prescaler” DS8629), já existir um cerâmico de 1 nF, para tal. No entanto, quando o sinal deste oscilador/isolador de VHF for acoplado a um amplificador de RF, deve-se atentar para a tensão contínua existente no emissor do BF494/5 (um pouco inferior aos 9V do circuito): se a etapa seguinte for, por exemplo, a base de um transistor já polarizada pelo circuito do amplificador (por um divisor resistivo de tensão próprio), deve ser inserido um capacitor cerâmico de isolamento, entre 10 e 100 pF, tipicamente. No entanto, se a base deste posterior transistor já tiver sido projetada para receber como “bias” tanto o sinal de RF, quanto uma pequena tensão contínua, para polarizá-la, o acoplamento deve ser direto, sem o referido capacitor. De qualquer modo, o acoplamento de RF deve ser feito por cabo blindado ou coaxial de boa qualidade, com a malhas devidamente aterradas nas blindagens das duas placas de circuito impresso, para que não seja irradiado (e, portanto, para não sofrer perda de amplitude e/ou tender a causar instabilidades no equipamento) antes de chegar ao amplificador ao qual este circuito será conectado. Tal cuidado, de se utilizar cabo coaxial (de áudio ou RF) entre as placas de circuito impresso, também deve ser observado nas conexões entre a placa do VCO/“buffer”, e a do PLL.

2- SINTETIZADOR PLL

No sintetizador, cujo diagrama elétrico é demonstrado pela figura 2, vemos que o sinal de VHF advindo do “buffer” e do VCO é acoplado, via capacitor cerâmico de 1 nF, para isolamento de tensão contínua, ao pino do 7 do CI DS8629, um “prescaler” de tecnologia ECL da National Semiconductor, responsável por dividir por 100 a frequência que lhe é entregue e, também, atuar como disparador de Schmitt, já que, independentemente da forma do sinal que lhe chega, a sua saída (pino 2) sempre será digital. Como a alimentação deste CI deve ficar ente 4,5 e 5,5 V, foi inserido um regulador LM7805 (ou equivalente) como regulador de tensão; tal regulador deverá ser montado em um bom dissipador de calor (como demonstra o esquema), devido ao fato de dissipar, no mínimo, 700 mW, em razão do produto da diferença de tensão entre o +B do transmissor e os 5 V de saída do regulador, pela corrente drenada pelo PLL (no mínimo, 100 mA, consumo típico do DS8629; os demais CIs do PLL, por serem CMOS, têm consumo mínimo, de poucos mA – somados os três -, de sorte que a intensidade de corrente total drenada pelo sintetizador praticamente se concentra no referido “prescaler”).

Como os três protótipos montados se destinaram à faixa comercial de FM, vamos utilizá-los para explicar o funcionamento do circuito. Assim, o “prescaler” receberá sinais analógicos entre 87,5 e 108, MHz e os dividirá por 100. Para efeito de exemplo, tomemos 102,4 MHz (é claro que esta frequência não deve ser emitida para além dos limites da residência de quem operará o transmissor, primeiro, para não caracterizar “rádio pirata”, segundo porque é de dígito par após a vírgula, o que é contrário ao padrão de FM do Brasil e da maioria dos países do mundo): ao recebê-lo, o DS8629 o dividirá por 100 e lhe entregará, digital, sob a frequência de 1024 KHz.

Ao mesmo tempo, a porta lógica osciladora do HEF4060, ou CD4060 (pinos 10 a 12), geram um sinal digital de 4,096 MHz, de alta estabilidade e precisão, devido ao cristal de quartzo de mesma frequência nela conectado (para provar a existência deste sinal, se o montador – assim como eu – não dispuser de frequencímetro e nem de osciloscópio, basta soldar um pequeno pedaço de fio rígido no pino 11 do 4060, e sintonizar o seu sinal em um receptor de ondas tropicais ou curtas, que o receberão na fundamental, 4096 kHz, e em seus harmônicos, 8192, 16384, etc., ou ainda, com muito menor amplitude – daí a necessidade de se aproximar bastante o receptor -, os harmônicos (vigésimo segundo a vigésimo sexto) na faixa de FM: 90,1, 94,2, 98,3, 102,4 e 106,5 MHz; se possível, utilize um receptor digital de FM para este teste: se o oscilador gerar os 4096 kHz, com exatidão (e o faz, pois os capacitores de 39 pF levam o cristal à precisa vibração da frequência para a qual foi cortado, sem – pequenos – desvios), “soltando-se” a sintonia digital automática (“scan”) do rádio receptor, o PLL dele fará o display “parar” nestas frequências acima mencionadas: 90,1, 94,2...e 106,5 MHz; se necessário, enrole o fio que vem do pino 11 do 4060 à antena do receptor de FM, para tal, pois a amplitude dos harmônicos digitais, oriundos de um sinal de frequência bem menor – 4,096 MHz – é muito baixa, para que sejam sintonizados por um rádio FM. Além de um oscilador interno, o CI 4060 também conta com 10 flip-flops, cada qual correspondente a um divisor binário, conforme ilustra a tabela, abaixo:

| HEF4060 | ||

| Pino | Função | |

| 1 | divide por | 4096 |

| 2 | divide por | 8192 |

| 3 | divide por | 16384 |

| 4 | divide por | 64 |

| 5 | divide por | 32 |

| 6 | divide por | 128 |

| 7 | divide por | 16 |

| 8 | alimentação | GND |

| 9 | saída inversor | -clock |

| 10 | saída oscilador | clock |

| 11 | entrada oscilador | reset |

| 12 | terra do oscilador | MR |

| 13 | divide por | 512 |

| 14 | divide por | 256 |

| 15 | divide por | 1024 |

| 16 | alimentação | VDD |

Para o nosso projeto, foi utilizado o nível “Q 11”, flip-flop correspondente ao pino 1 que, de acordo com o “datasheet” dos fabricantes do CI, corresponde a 211+1, ou seja, 4096. Como o cristal utilizado é de 4,096 MHz, da saída do flip-flop escolhido temos, portanto 4096 kHz divididos por 4096 (212), ou seja, 1 kHz. A escolha desta frequência, como referência para a porta “EXOR” (“ou exclusivo”) de um dos dois comparadores de fase internos ao HEF4046 foi proposital pois, como sabemos, o número 1 (no caso, um mil) é o divisor universal. Assim, se a frequência advinda do DS8629 (1% da fundamental, de oscilação livre, gerada pelo VCO), em kHz, for dividida por seu próprio valor através do divisor lógico programável em torno do HEF4040, no pino de reset dele também haverá 1000 Hz, que serão levados, como amostra, à outra entrada do detector do 4046, pelo pino 3. Assim, toda a vez em que a frequência de amostra (variável e aleatória) ficar próxima da de referência (de 1 kHz, fixa, precisa e estável, por advir de oscilador a quartzo), teremos na saída da porta “ou-exclusivo” do 4046 (pino 13) o nível “1”, ou seja, uma determinada tensão de erro, proporcional à diferença de fase e frequência dos sinais entregues à suas duas entradas. Tal tensão, se devidamente filtrada (por possuir uma forte componente alternada), de modo que a sua frequência fique o mais próxima de zero Hz (corrente contínua pura), poderá ser retornada ao VCO, através dos diodos varactores (varicaps) que fazem parte do seu circuito de ressonância, de modo a forçá-lo a gerar a frequência que programarmos no divisor lógico por “n”, em BCD. Assim, para o exemplo citado, 102,4 MHz, basta levar a “1” o nível “K” (Q 11) do HEF4040, alimentando-se o seu respectivo diodo, através de um “jumper” de placa de computador, ou de chave “dip switch”: o 4040, neste caso, dividirá por 1024 o sinal aleatório (entre 875 e 1080 kHz) que recebe do DS8629; o 4046, por seu turno, “sente” a “proximidade” entre a frequência fixa de referência (1 kHz, no pino 14) e a de amostra, entre 854,49 e 1,055 KHz, e envia, instantaneamente, uma tensão de erro de controle automático de frequência (CAF ou “AFC”) em seu pino 13, a qual fará os varactores aumentarem ou reduzirem suas capacitâncias, até que o 4046 “sinta” que a frequência aplicada na sua entrada de sinal de amostra (pino 3) se igualou àquela entregue como referência (1 kHz fixo, a quartzo, aplicada no pino 14). Assim, indiretamente, o 4046 força o VCO a gerar 102,4 MHz, pois: 102,4 MHz divididos por 100 (DS8629) geram 1,024 MHz; estes, por sua vez, dividos por 1024 pelo 4040, geram 1 vezes 10-3 MHz, ou seja, 1 kHz. Quando isto acontecer, é porque o PLL amarrou o sistema (o que se comprova pelo brilho máximo do LED ligado ao pino 1 do 4046), não só forçando o VCO a gerar 102,4 MHz, como também comparando-os, o tempo todo, com o sinal de referência de 1 kHz: caso no seu pino 3 haja qualquer diferença, por menor que seja, entre o sinal digital que nele é entregue, e o de referência, que é de 1 kHz, o 4046, imediatamente, alterará o “AFC”, para mais ou para menos, para nova amarração. Como a frequência de referência é de 1 kHz, o comparador de fase deste CI faz esta correção mil vezes por segundo, ou seja, instantaneamente. Para provar a eficiência e funcionamento do sistema, basta querer se alterar a estabilidade do VCO, tocando-se a sua bobina e/ou capacitores do circuito ressonante próximos: o PLL então “entra em alerta”, faz piscar o LED ligado ao seu pino 1, e corrige o erro (induzido) de frequência. A prova maior disto é soltar a sintonia automática (“scan”) de um receptor digital de FM, nas proximidades: ele “parará” em 102,4 MHz, independemente de haver ou não modulação no transmissor, ou de se alterar, por exemplo, a indutância da bobina do VCO, apertando-a ou alargando-a. Nota: quando o transmissor é ligado e, cerca de 2 segundos após (tempo que ele leva para sincronizar o PLL), um pequeno e breve apito é ouvido nos falantes do rádio, evidenciando que o transmissor travou.

É claro que, assim como a grande maioria dos países do mundo, o Brasil utiliza o padrão ímpar para emissão de FM, na primeira “casa” após a vírgula; assim, uma vez conseguidos os 102,4 MHz estabilizados, o alteremos para 102,5; para tal, basta fechar a chave (“dip” ou “jumper”) do nível “Q 0”, ou “A”, que corresponde ao diodo conectado ao pino 9 do 4046: o LED do PLL piscará brevemente e, menos de 1 segundo depois, o sistema gerará 102,5 MHz: novamente, pode-se “soltar” o “scan” do rádio digital que, agora, “parará” em 102,5, tanto “para cima” (“up”), como “para baixo” (“down”). Para provar a rapidez com a qual o PLL amarra, se, por exemplo, for fechado, também, o nível “Q 6” (“F”), correspondente ao diodo que alimenta o pino 2 do 4040, o sistema somará 32 aos 1025 já programados, o que levará o PLL a gerar 105,7 MHz; se o nível “Q 0” for desabilitado, serão gerados, imediatamente, 105,6 MHz. Enfim, para se gerar a frequência desejada, basta “tirar” a vírgula do seu valor em MHz, e “digitá-la”, em BCD, nos “jumpers” ou chaves “dip switch” ligadas aos diodos do 4040; contato aberto: nível “0”, contato fechado: nível “1”. E, de fato, para os 105,7 MHz exemplificados, temos: 1024 (“K”) + 32 (“F”) + 1 (“A”), ou Q 11 + Q 6 + Q 0, em BCD.

Notas:

1- Pelo fato de ser alimentado com 5 V, o sintetizador tem 2,5 V como nível alto (esta será a tensão existente nas saídas de todos os divisores, “flip-flops”, do 4060); porém, quando o divisor lógico (constituído pelo HEF4040 e diodos nele conectados) é programado, o terminal de “reset” (pino 11) entrega cerca de 1,2 V ao pino 3 do 4046; este, porém, o “detecta” como nível alto (“1”);

2- O capacitor cerâmico de 47 pF (valor obtido experimentalmente) conectado entre o “reset” (pino 11 do 4040) e a terra, é de suma importância, pois a sua inexistência poderá levar o divisor lógico programável a gerar algumas divisões completamente diferentes do valor binário que nele colocamos; além disto, em alguns casos, sem o tal capacitor, há programações que o próprio divisor “rejeita”, de modo a não sincronizar o PLL (o LED nem chega a acender). Se o leitor, ao montar o circuito, quiser prová-lo, basta, inicialmente, deixar de soldar o referido capacitor na placa do PLL, para verificar que certas frequências (como 107,1, 107,3, 106,7, 107,5 e 107,7 MHz) não serão geradas, produzindo-se outras menores e completamente diferentes (muito embora o PLL trave)! Após a conexão dele ao circuito, o divisor lógico programável funcionará perfeitamente, “obedecendo” a qualquer divisão binária que nele impusermos;

3- O VCO, conforme podemos ver pelo diagrama da figura 1, tem, em paralelo com a bobina, um capacitor (cerâmico, ou, melhor ainda, plate NPO ou de mica prateada) de 2,2 pF; se a bobina L tiver 4 espiras, com diâmetro de 6 mm e comprimento de 1 cm, o PLL facilmente “varrerá” as maiores frequências da faixa de FM, acima de 95 MHz; no entanto, caso o divisor lógico seja programado para, por exemplo, dividir por 901 (“I”+ “H”+ “G”+ “C” + “A”), para gerar 90,1 MHz, e o PLL não amarre, aumente a bobina para 5 espiras e/ou o capacitor em paralelo, para valores entre 4,7 e 10 pF; do modo originalmente projetado, com L sendo constituída por 4 espiras, foi gerada, fácil e instantanemente, quaquer frequência maior que 95 MHz (até 109 MHz ele “aceitou” pois, muito embora eu não tenha receptores para esta faixa, percebi que o LED acendeu fortemente e que, tocando-se a bobina, o 4046 o fez piscar por alguns instantes, indicando que amarrou o VCO); nestas condições, entre 95 e 109 MHz, bastou-se alterar o fator “n” do divisor lógico programável, para que o transmissor sincronizasse imediatamente, sem ser necessário apertar ou alargar as espiras de L. Aliás, gerando-se, por exemplo, 105,7 MHz (“K”+ “L”+ “A”) e, retirando-se o “jumper” de computador que alimentava o nível lógico “L” (Q 6 = divisor por 32), imeditamente o VCO e o sintetizador geraram 102,5 MHz (com sincronização imediata: quem “demorou” fui eu e meus receivers, digital – “Gradiente Spect 90” - e analógico – “Gradiente S-95”, à procura da nova frequência gerada!);

4- Novamente, não custa lembrar que, assim como a placa do VCO/“buffer”, também a do PLL deve ser blindada, envolta por “gaiola de Farad”soldada à terra, cuja trilha deverá ser grossa (5mm, no mínimo) e contornar todo o circuito, no perímetro de toda a placa; estas blindagens protegem o VCO de ser modulado por ruídos digitais gerados pelo sintetizador e, ao mesmo tempo, também evitam que este receba campos eletromagnéticos externos (como a própria RF gerada pelo transmissor), os quais poderiam levá-lo à instabilidade, vindo a não sincronizar (afinal, vale lembrar que, nele, há três CIs que utilizam tecnologia CMOS e, como tais, são altamente sensíveis, devido às altas impedâncias de entrada de suas portas lógicas; ainda sobre estes integrados, e o próprio “prescaler” DS8629, não é redundante o aviso de que devem ser montados em soquetes, para evitar que o calor e/ou fugas de tensão de ferros de solda os danifiquem; com relação ao DS8629, é normal o fato de trabalhar com um considerável aquecimento, posto que dissipa meio watt de potência, por drenar entre 90 e 100 mA de corrente, sob os seus nominais 5V de alimentação. Assim, o único CI que deve ser dotado de um dissipador de calor é o 7805.

5- Conforme demonstra o diagrama elétrico, os capacitores ligados ao cristal devem ser, preferivelmente, plate NPO, ou de mica prateada. No entanto, o uso de cerâmicos comuns, de boa qualidade, em nada impedirá o perfeito funcionamento do transmissor; a questão é que, como podem promover um pequeno desvio (alguns Hz) na frequência do cristal de quartzo, o sinal gerado pelo oscilador do 4060 pode ficar ligeiramente diferente de 4,096 MHz, implicando, para o 4046, uma referência um pouco diferente de 1 kHz (como 999 ou 1001 Hz, por exemplo); isto faria com que, por exemplo, em vez de 107,5 MHz (divisor programado para dividir por 1075, no CI 4040), fosse gerada uma frequência de 107,49999 ou 107,50001 MHz: é claro que tal não impedirá que rádios receptores digitais sintonizem o transmissor, e também está “dentro” das normais internacionais de radiodifusão comercial de FM, que “toleram” até 2 kHz de erro sobre a frequência da portadora, para mais, ou para menos; porém, se o leitor dispuser de um frequencímetro, seria muito interessante a geração exata das frequências produzidas pelo transmissor, o que pode ser constatado, através do referido equipamento de medição, ou pela indicação de exatos 1000 Hz advindos do 4060 (pino 1), ou pela indicação da própria portadora de VHF gerada pelo modulador: seja por uma, seja por outra avaliação, os capacitores de 39 pF podem ser alterados, até que se consiga a melhor precisão de portadora gerada pelo PLL e pelo VCO; o uso de um “trimmer” no lugar de um destes dois capacitores também é possível, mas deve-se atentar para a sua qualidade, para que não se altere a sua capacitância, por motivo de temperatura, por exemplo. Porém, de qualquer modo, o simples emprego dos dois capacitores de 39 pF já dá alta precisão, ao transmissor.

6- Por fim, vemos um outro cuidado que foi tomado no projeto do sintetizador: um elaborado filtro passa-baixas, entre o pino 13 do 4046 (saída do detector de fase) e o cabo blindado, que conduzirá o AFC produzido, aos varicaps do VCO: tal filtro, como podemos ver, se constitui de: a) um filtro RC (10 K? em série com 33 nF, preferivelmente de poliéster), com frequência de corte em torno de 482 Hz, menos da metade dos 1000, que é a base de tempo do PLL; isto foi proposital para que, sob 1 kHz, este filtro RC o atenue mais intensamente (pois, como sabemos, estes filtros RC não são abruptos, por terem uma grande largura de banda); b) três constantes de tempo (integrador RC, de 10 K? e 10 µF ) de 0,1 segundo, em paralelo com o AFC, além de uma última, final, de cerca 0,047 segundo (10 K? e 4,7 µF): estas constantes atenuam bastante a forte componente alternada advinda da saída do 4046 pois, justamente pelo fato de serem integradores RC, a “prioridade” para o sinal é carregar os eletrolíticos de 4,7 e 10 µF, antes de chegar à saída. Note-se, também, os dois diodos em antiparalelo entre si, e em paralelo com um resistor de 33 K?, entre os dois primeiros integradores: temos, deste modo, um “clipper”, que ceifa os dois picos de -0,7 e +0,7 V existentes no sinal advindo do 4046, o que, em muito, também contribui para eliminar o forte ruído produzido pelo detector de fase; por outro lado, como os diodos proporcionam uma queda considerável de amplitude ao AFC, impedindo o PLL de sincronizar, há, em paralelo, o resistor de 33 K?, para que tal não ocorra; c) vários capacitores cerâmicos de 100 nF, desacoplando tanto a indevida indutância destes pequenos capacitores eletrolíticos, como também eliminando sinais de alta frequência de áudio advindos do detector de fase (como apitos, muito comuns em transmissores PLL com filtros ruins), para que não cheguem ao VCO; para esta função, como filtro final, também está o de poliéster de 220 nF, em paralelo com a saída. Todos estes cuidados garantem a produção de um AFC limpo, sem resíduos de tensão alternada, só vindo a ter variação em sua amplitude, justamente para estabilizar o VCO. Como, por definição, os diodoos varactores, ou varicaps, trabalham em polarização reversa, tendo suas capacitâncias inversamente proporcionais à tensão sobre eles aplicada, obviamente o AFC é diretamente proporcional à frequência que o PLL gerará (e vice-versa); no esquema, como foram utilizados os mesmos varicaps tanto para receber o AFC, como para receber a própria modulação, ocorre o inconveniente de, conforme se aumenta a frequência transmitida, o índice de modulação diminuir, pelo fato de o AFC aumentar, e vice-versa. Para tal, uma sugestão de se acoplar um terceiro varicap, independente e com tensão fixa, é dada na figura 3. Mas, geralmente isto não se faz necessário, bastando-se, simplesmente, se aumentar (ou diminuir) a amplitude do sinal modulante, de modo proporcional ao AFC e, consequentemente, à frequência gerada.