Em todo sistema em que dados digitais devam ser transmitidos e recebidos na forma serial, existe um elemento importante presente, que deve ser entendido pelos profissionais das telecomunicações: as UARTs. Com a finalidade de converter dados paralelos para a forma serial e vice versa, as UARTs estão presente nos modems e em muitos outros equipamentos. Veja neste artigo como elas funcionam e como são usadas.

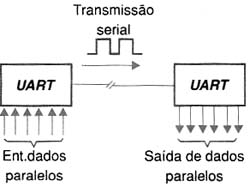

UART é o acrônimo de Universal Asynchrounous Receiver/Transmiter ou Receptor/Transmissor Universal Assíncrono. Sua finalidade é possibilitar a transmissão e a recepção de dados originalmente disponíveis na forma paralela, conforme mostra a figura 1.

No diagrama de funcionamento, pode parecer simples, converter os dados que chegam ao mesmo tempo nas entradas paralelas de modo que eles sejam transmitidos seqüencialmente por uma linha de dados e depois, recuperá-los recebendo-os em seqüência e apresentados na forma paralela na saída

No entanto, precisamos levar em conta que essa transmissão deve ser feita de modo seguro, com um controle de paridade para garantir a integridade dos dados e formas de sinalização do lado que transmite para que o lado que recebe saiba onde começa e onde termina uma transmissão. Tudo isso é justamente feito pelas UARTs que tem sido usada a um bom tempo, conforme veremos a seguir.

Os tipos de UARTs

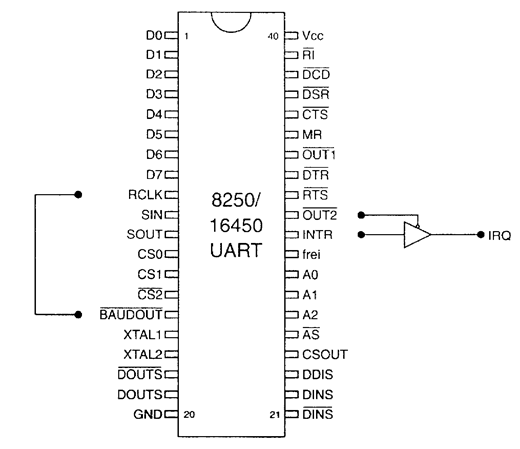

As primeiras UARTs usadas nos computadores (PCs) eram do tipo 8250 empregadas basicamente na série XT. Posteriormente, novos tipos foram criados como a 8250A, 8250 B e em seguida a 16450. Essa última foi implementada nos computadores da série AT. Na figura 2 temos o invólucro dessa UART de 40 pinos.

Figura 2 – UART 16450

A cada tipo lançado, o principal implemento era a velocidade de operação. Assim, a 16450 já alcançava uma velocidade de 38,4 kbp facilmente. Mas mesmo assim, para as exigências crescentes dos novos computadores essa velocidade logo se tornou pequena. Surgiu então a 16550 que resolvia um problema que começava a incomodar.

Os tipos anteriores precisavam ter uma ação do software a cada bit que transmitiam. A 16550 continha buffers FIFO on board que podiam armazenar cada um 16 bits, um para os sinais trasmitidos e outro para os recebidos.

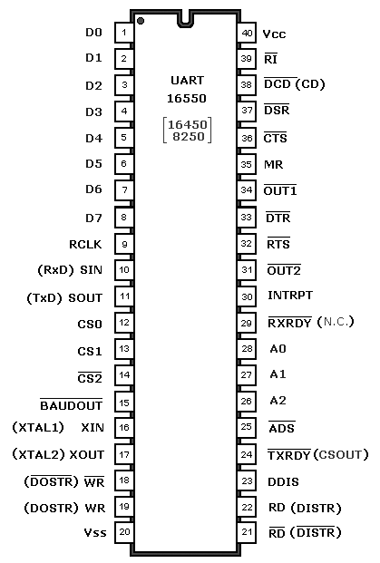

No entanto, um “bug” tornava impossível usar esses buffers até que surgiu a 16550A capaz de transmitir a uma velocidade de 115,2 kbps.

Figura 3 – A pinagem da 16550A.

Essa UART podia ter usar a DMA (Direct Access Memory) para a transmissão de dados, de modo a não exigir a intervenção do software para essa finalidade. Hoje, a 16550A é a UART mais comum, contendo 32 bytes de FIFO e software de controle para garantir o fluxo de dados.

A Texas Instruments tem uma UART de 64 bytes de FIFO, denominada 16750.

A Estrutura de uma UART

Para que uma UART funcione existem diversos tipos de circuitos funcionamento de modo coordenado. Vejamos quais são esses circuitos.

Registradores

São usados 8 bytes I/O para cada UART com a finalidade de acessar os registros. A tabela abaixo mostra onde cada registro está.

|

Tabela de Conversão Registro para Porta de UART |

||||

|

|

DLAB = 0 |

DLAB = 1 |

||

|

Porta I/O |

Ler |

Gravar |

Ler |

Gravar |

|

Base |

RBR |

THR |

DLL divisor latch LSB |

|

|

base + 1 |

IER |

IER |

DLM divisor latch MSB |

|

|

base + 2 |

IIR |

FCR |

IIR |

FCR |

|

base + 3 |

LCR controle de linha |

|||

|

base + 4 |

MCR controle de modem |

|||

|

base + 5 |

LSR |

– |

LSR |

– |

|

base + 6 |

MSR |

– |

MSR

|

– |

|

base + 7 |

SCR scratch |

|||

Analisemos cada um desses registros e sua função:

RBR – Receiver Buffer Register (RO)

A finalidade desse registro é armazenar o byte recebido se nenhum FIFO é usado ou o último byte não lido. Se o buffer da FIFO é sado, cada nova ação de leitura do registro passa para o byte seguinte até que nenhum byte esteja presente. O byte 0 na linha de status do registro pode ser usado para verificar se os bytes recebidos foram lidos.

Obs: RO significa Read Only ou apenas leitura.

THR: Transmiter Holding Register (WO)

É usado para os caracteres que saem do buffer. Se a FIFO não é usada, somente um caractere pode ser armazenado. Se usada, a quantidade de caracteres armazenados depende da UART. O THR não é usado para transmitir dados diretamente. O byte é inicialmente transferido para um shift register onde a informação é dividida em bits para transmissão uma a um.

Obs: WO significa Write Only ou apenas gravação

IER: Interrupt Enable Register (R/W)

Uma forma eficiente de se conseguir comunicações entre PCs na forma serial é utilizando rotinas de interrupção. Nessa configuração, não é necessário colocar os registros da UART periodicamente em estado de mudança. A UART vai sinalizar a cada mudança gerando uma interrupção para o processador. Uma rotina de software pode então ser usado para manusear a interrupção e verificar qual estado de mudança a gerou.

As interrupções não são geradas a não ser que a UART seja avisada. Isso é feito enviando-se bits para o registro de habilitação da interrupção. O bit 1 indica que uma interrupção deve ser feita. A tabela abaixo mostra esses bits.

|

Bit |

Comentário |

|

0 |

Dados recebidos disponíveis |

|

1 |

Registro de controle do transmissor vazio |

|

2 |

Mudança de estado do registro linha |

|

3 |

Mudança do estado do registro de modem |

|

4 |

Modo sleep (somente na 16750) |

|

5 |

Modo de baixo consumo (somente na 16750) |

|

6 |

Reservado |

|

7 |

Reservado |

Obs) R/W significa Read/Write ou Leitura e Gravação

IIR: Interrupt Identification Register (RO)

Trata-se do registro de identificação de interrupção. Uma UART pode gerar uma interrupção de processador quando uma mudança no dispositivo de comunicação é detectada. Esse sinal é usado para chamar a atenção antes do envio das informações. Seus bits mostram o estado da UART e qual a mudança de estado fez com que a interrupção ocorresse. A tabela abaixo mostra os significados dos bits desse registro:

|

IIR :Registro de Identificação de Interrupção |

||||||

|

Bit |

Valor |

Descrição |

Reset por |

|||

|

0 |

0 |

Interrupção pendente |

– |

|||

|

1 |

Nenhuma interrupção pendente |

– |

||||

|

1,2,3 |

Bit 3 |

Bit 2 |

Bit 1 |

|

|

|

|

0 |

0 |

0 |

Mudança de estado do Modem |

MSR lido |

||

|

0 |

0 |

1 |

Registro do transmissor vazio |

IIR lido ou THR gravado |

||

|

0 |

1 |

0 |

Dados recebidos disponíveis |

RBR lido |

||

|

0 |

1 |

1 |

Mudança de estado da linha |

LSR lido |

||

|

1 |

1 |

0 |

timeout de caractere (16550) |

RBR lido |

||

|

4 |

0 |

Reservado |

– |

|||

|

5 |

0 |

Reservado (8250, 16450, 16550) |

– |

|||

|

1 |

FIFO de 64 byte habilitada (16750) |

– |

||||

|

6,7 |

Bit 7 |

Bit 6 |

|

|

||

|

0 |

0 |

Nenhuma FIFO |

– |

|||

|

1 |

0 |

FIFO não usada (16550 apenas) |

– |

|||

|

1 |

1 |

FIFO habilitada |

|

|||

FCR: FIFO Control Register (WO)

É o registro de controle da FIFO que controla o comportamento da FIFO na UART. O valor lógico 1 e gravado nos bits 1 ou 2 e sua função é disparar o dispositivo. Outros bits são usados para selecionar o modo específico de funcionamento. A tabela abaixo mostra como os diversos bits são usados.

|

FCR : FIFO control register |

|||

|

Bit |

Valor |

Descrição |

|

|

0 |

0 |

Desabilitação da FIFO |

|

|

1 |

Habilitação da FIFO |

||

|

1 |

0 |

– |

|

|

1 |

Apaga a FIFO de recepção |

||

|

2 |

0 |

– |

|

|

1 |

Apaga a FIFO de transmissão FIFO |

||

|

3 |

0 |

Seleciona o modo 0 da DMA |

|

|

1 |

Seleciona o modo 1 da DMA |

||

|

4 |

0 |

Reservado |

|

|

5 |

0 |

Reservado (8250, 16450, 16550) |

|

|

1 |

Habilita a FIFO de 64 byte FIFO (16750) |

||

|

6,7 |

Bit 7 |

Bit 6 |

Recebe o nível de disparo de interrupção da FIFO |

|

0 |

0 |

1 byte |

|

|

0 |

1 |

4 bytes |

|

|

1 |

0 |

8 bytes |

|

|

1 |

1 |

14 bytes |

|

LCR: Line Control Register (R/W)

Esse registro é usado na inicialização para fixar os parâmetros da comunicação. Paridade, número de bits de dados podem ser alterados. Esse registro também controla a acessibilidade dos registros da DLL e DLM. Como esses registros são acessados apenas no processo de inicialização eles não influem na performance da UART.

Os modos de ajuste mais comuns são:

· 8 bits de dados, um bit de parada, sem paridade

· 7 bits de dados, uma parada, paridade ímpar

|

LCR : Registro de Controle de Linha |

|||||

|

Bit |

Valor |

Descrição |

|||

|

0,1 |

Bit 1 |

Bit 0 |

Comprimento da palavra de dados |

||

|

0 |

0 |

5 bits |

|||

|

0 |

1 |

6 bits |

|||

|

1 |

0 |

7 bits |

|||

|

1 |

1 |

8 bits |

|||

|

2 |

0 |

1 stop bit |

|||

|

1 |

1.5 stop bits (palavra de 5 bits ) |

||||

|

3,4,5 |

Bit 5 |

Bit 4 |

Bit 3 |

|

|

|

x |

x |

0 |

Sem paridade |

||

|

0 |

0 |

1 |

Com paridade par |

||

|

0 |

1 |

1 |

Com paridade ímpar |

||

|

1 |

0 |

1 |

Alta paridade (stick) |

||

|

1 |

1 |

1 |

Baixa paridade (stick) |

||

|

6 |

0 |

Sinal de Break desabilitado |

|||

|

1 |

Sinal de Break habilitado |

||||

|

7 |

0 |

DLAB : RBR, THR e IER accessíveis |

|||

|

1 |

DLAB : DLL e DLM accessíveis |

||||

MCR: Modem Control Register (R/W)

|

MCR : Registro de Controle do Modem |

|

|

Bit |

Descrição |

|

0 |

Terminal de dados pronto |

|

1 |

Pedido para transmitir |

|

2 |

Saída Auxiliar 1 |

|

3 |

Saída Auxiliar 2 |

|

4 |

Modo Loopback |

|

5 |

Controle Autoflow (16750 somente) |

|

6 |

Reservado |

|

7 |

Reservado |

As duas saídas auxiliares são definíveis pelo usuário. A saída 2 é usada, algumas vezes no circuito que controle o processo de interrupção de um PC. A saída 1 é normalmente usada em placas I/O, selecionando a freqüência de um segundo oscilador que opera em 4 MHz. Normalmente é usada em aplicações MIDI.

LSR: Line Status Register (RO)

Essa registrador mostra o estado da comunicação, detectando erros. A tabela abaixo mostra o significado dos bits nesse registro.

|

LSR : Line status register |

|

|

Bit |

Descrição |

|

0 |

Dados disponíveis |

|

1 |

Erro de Overrun |

|

2 |

Erro de paridade |

|

3 |

Erro de Framing |

|

4 |

Sinal Break recebido |

|

5 |

THR está vazia |

|

6 |

THR está vazia , e a linha está desocupada |

|

7 |

Dados errados na FIFO |

MSR: Modem Status register (RO)

O MSR armazena informações sobre as quatro linhas de controle do modem. A informação é dividida em dois nibbles. Os quatro bits mais significativos (MSB) contém informações sobre o estado das entradas enquanto os quatro bits menos significativos (LSB) são usados para indicar as mudanças de estado. A tabela abaixo mostra o significado dos bits desse registro.

|

MSR : Modem status register |

|

|

Bit |

Descrição |

|

0 |

Mudança no Clear to send |

|

1 |

Mudança no Data set ready |

|

2 |

Indicador do trailing edge Ring |

|

3 |

Mudança no Carrier detect |

|

4 |

Clear to send |

|

5 |

Data set pronto |

|

6 |

Idicador de Ring |

|

7 |

Detecção de Portadora |

SCR: Scratch Register (R/W)

A finalidade desse registro de gravação e leitura é armazenar um bit, mas na prática tem uso muito limitado. Como está presente apenas nas UARTs mais antigas, não é muito comum seu uso.

DLL e DLM: Divisor Latch Registers (R/W)

O ritmo de funcionamento da UART é determinado por um oscilador que opera em1,8432 MHz. Essa freqüência é dividida por 10 para gerar a base de tempo de todo o sistema que então alcança sua velocidade máxima de 115 200 bps.

Existem entretanto UARTs como a 16550 que podem até operar com freqüências mais altas, até 24 MHz, o que possibilita comunicações até 1,5 Mbps. No entanto, esses valores não são usados nos PCs por serem incompatíveis com as configurações de software.

A tabela abaixo mostra as possibilidades de se dividir a freqüência original e assim obter velocidades mais baixas de acordo com a capacidade do meio de comunicações usado.

|

DLL eDLM : Divisor latch registers |

|||

|

Velocidade (bps) |

Divisor |

DLL |

DLM |

|

50 |

2,304 |

0x00 |

0x09 |

|

300 |

384 |

0x80 |

0x01 |

|

1,200 |

96 |

0x60 |

0x00 |

|

2,400 |

48 |

0x30 |

0x00 |

|

4,800 |

24 |

0x18 |

0x00 |

|

9,600 |

12 |

0x0C |

0x00 |

|

19,200 |

6 |

0x06 |

0x00 |

|

38,400 |

3 |

0x03 |

0x00 |

|

57,600 |

2 |

0x02 |

0x00 |

|

115,200 |

1 |

0x01 |

0x00 |

Conclusão

As UARTs são os elementos básicos de qualquer sistema de comunicação serial. Elas formam o “coração” dos Modems possibilitando a transformação de dados na forma paralela para serial e vice-versa. Nesse artigo vimos como elas funcionam, dando uma idéia das funções que elas fazem e das diversas configurações possíveis para seus registros.