Os elementos imunes a ruídos LSL (Low Speed Logic) apresentam a vantagem de seus tempos de comutação poderem ser reduzidos por meio de um capacitor externo, o que assegura também uma imunidade aos ruídos. essa possibilidade pode ser aproveitada com vantagens nos circuitos de tempo em que haja presente um elevado nível de ruído.

Nota: Artigo da Revista Saber Eletrônica 48 de junho de 1976

Neste artigo, baseados no "Siemens Electronic Components Bulletin" (VII - 1972 -número 4), descrevemos circuitos de tempo (figura 1) que usam portas NAND LSL (FZH 111) e que podem ser empregados com as seguintes finalidades:

— Encurtamento de pulsos

— Retardamento de pulsos

— Monitoração de largura de pulsos

— Monitoração de frequência de pulsos

ELEMENTOS DE RETARDO

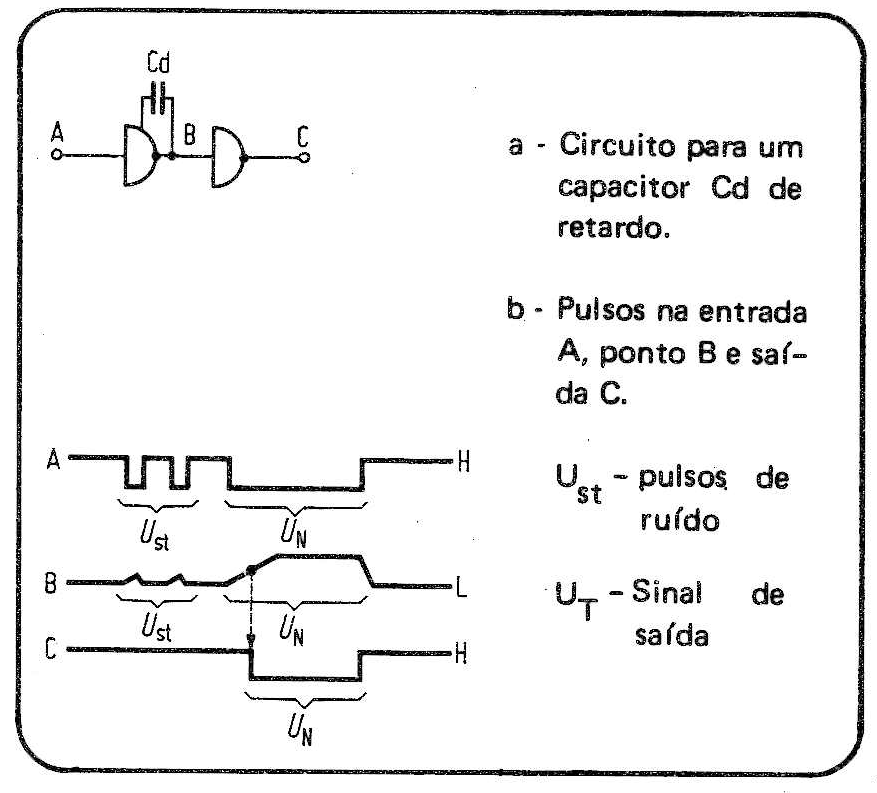

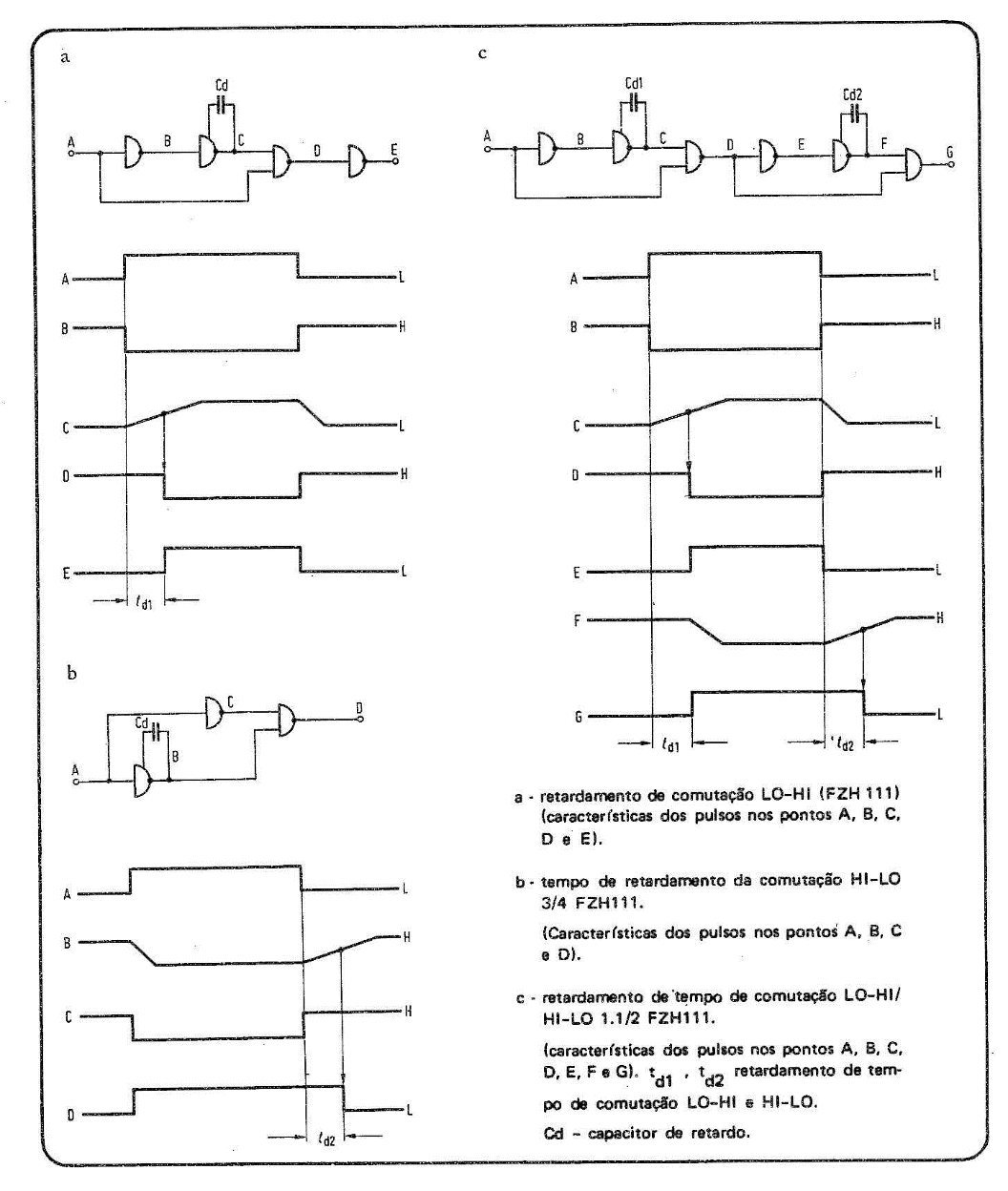

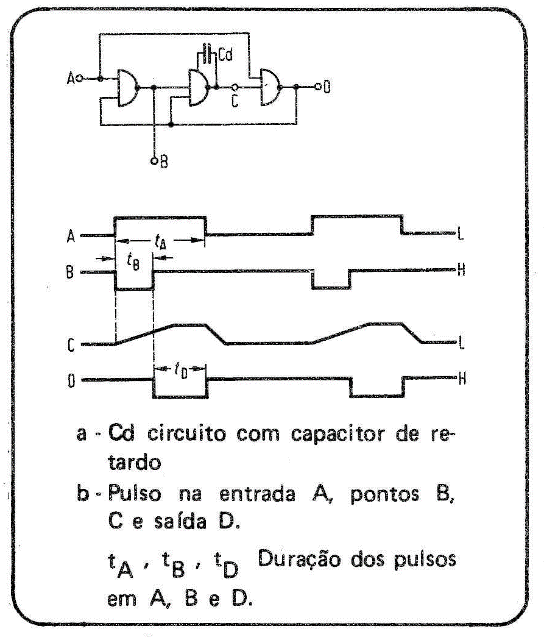

Na figura 2 ilustramos um circuito elementar no qual se obtém um retardamento no disparo, (a) ou um retardamento no desligamento (comutação LO-HI e H I- LO).

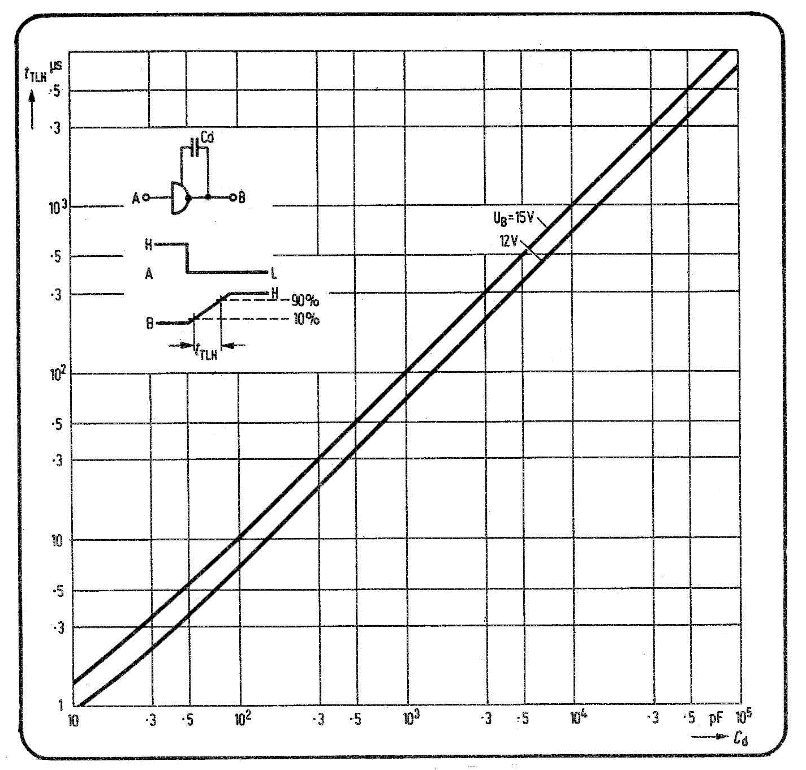

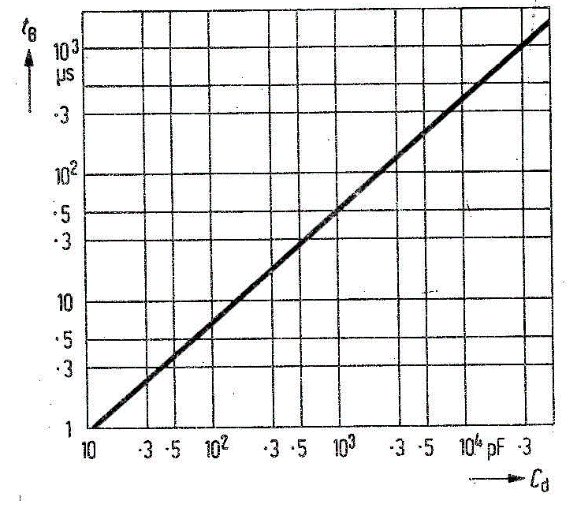

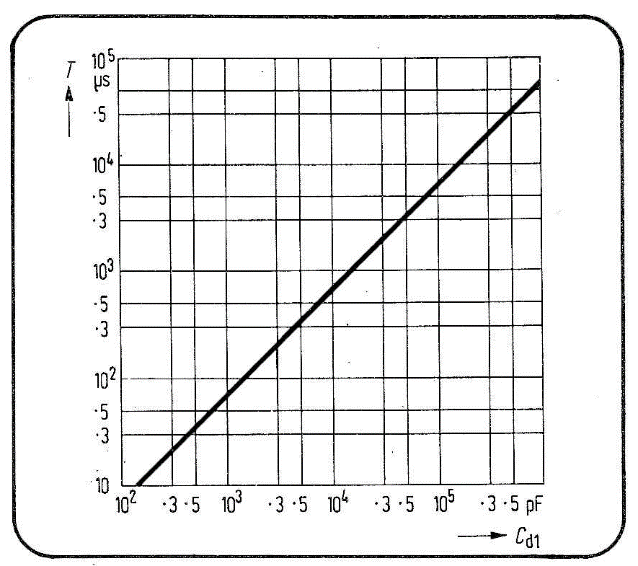

A figura 3 mostra a relação entre o -tempo de retardo e o valor do capacitor Cd, assim como o tempo de crescimento TLH. O tempo td de aproximadamente 50%, corresponde 'a excursão do elemento seguinte do circuito lógico, e do crescimento linear de tTLH como tempo (TLH = tempo de transição LO-HI).

ENCURTAMENTO OU ALONGAMENTO DE PULSOS

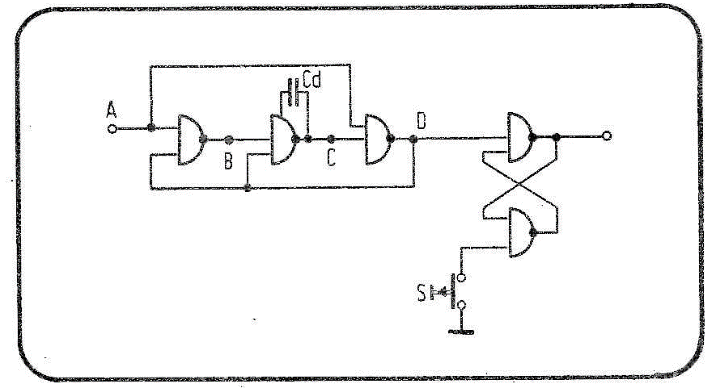

No circuito da figura 4, o capacitor Cd encurta os pulsos aplicados ao ponto 8 e prolonga a duração dos pulsos aplicados ao ponto D, conforme mostram os gráficos correspondentes.

A figura 5 vemos um gráfico em que é representada a duração do pulso de saída (tb) em função da capacitância Cd.

MONITOR DA LARGURA DE PULSOS

No circuito ilustrado na figura 6, a duração do pulso na entrada A é responsável pelo aparecimento de um pulso no ponto D. Para uma determinada duração do pulso de entrada ta (figura 4b), a duração (tb) do pulso invertido permanece constante. Com o aumento da duração do pulso de entrada (ta), os pulsos sofrem na saída um mesmo acréscimo de duração TD = ta - tb, aparecendo no ponto D. Quando, entretanto, TD excede determinado valor, um sinal Hl aparece na saída. A saída pode ser em seguida comutada ao nível LO por meio do interruptor S.

MONITORAÇÃO DE FREQUÊNCIA

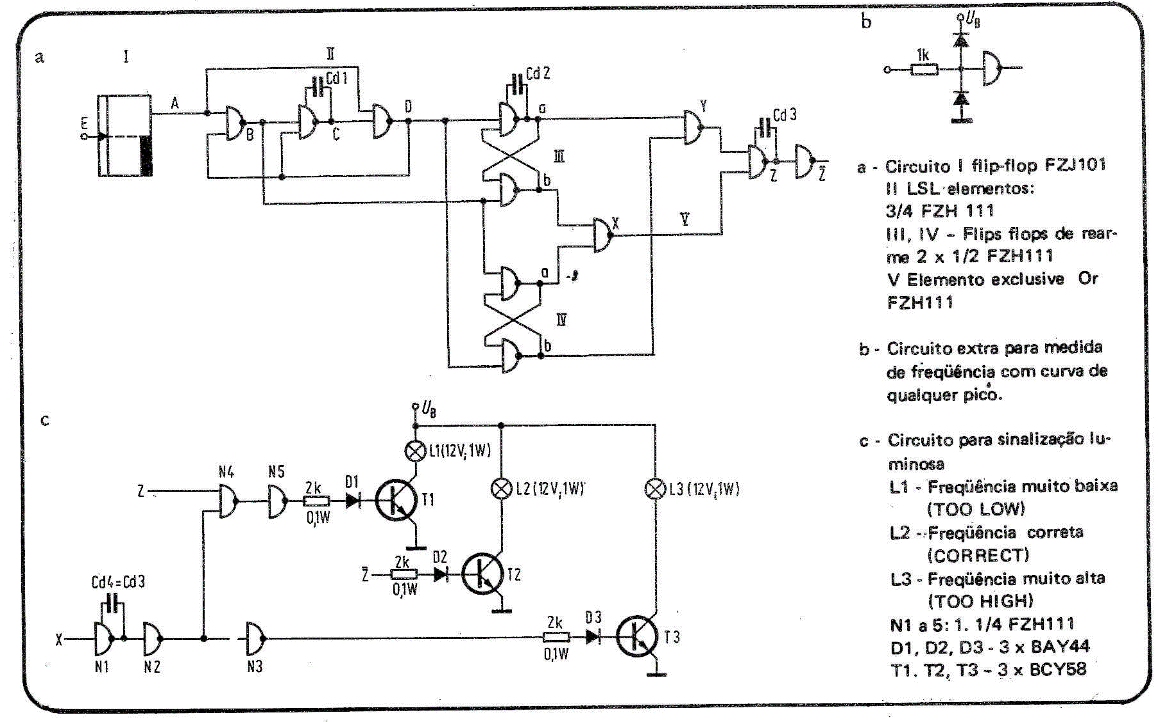

Atuando semelhantemente a um filtro de banda passante, o circuito da figura 7a pode ser usado na monitoração de uma frequência nominal entre dois limites pré-estabelecidos de tolerância. Na saída 2 obtém-se um sinal HI para uma determinada gama de frequências que pode ser estabelecida em função dos valores dos capacitores Cdl e Cd2, aparecendo um sinal LO para frequências fora dessa gama.

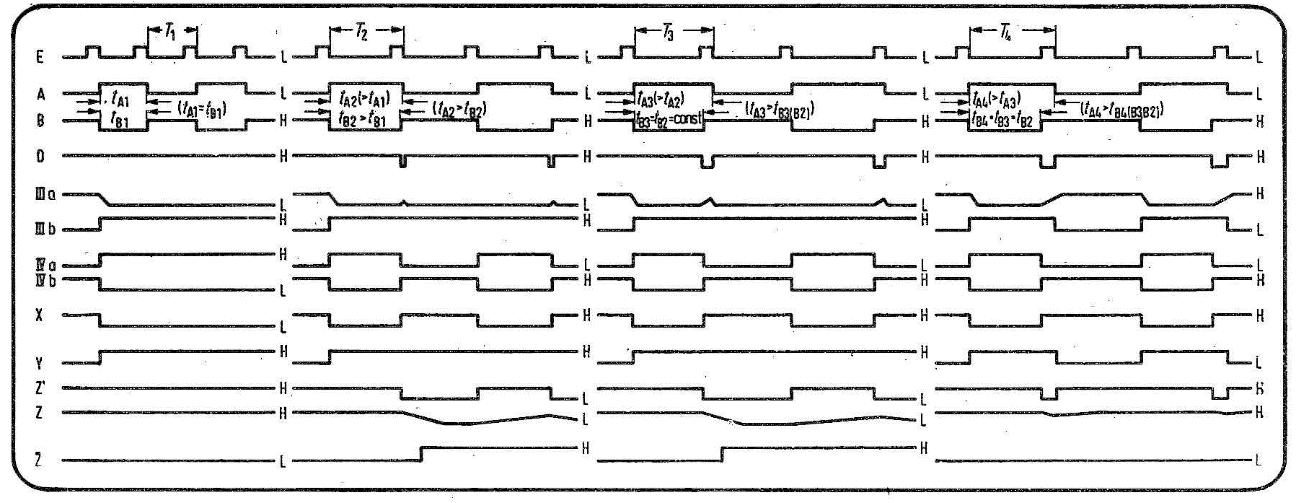

O "flip-flop" 1 reduz a série de pulsos na entrada E de uma relação de 2:1 (figura 8, linhas E e A). Se a frequência muda de um valor mais elevado para um valor mais baixo (aumento da duração do período T, figura 8, linha E), a duração ta dos pulsos na entrada A do elemento LSL II aumenta de ta = tb (tb é a duração do pulso invertido em B).

E: Na saída E do flip-flop I

A, B, D: nos pontos A, B e D do elemento LSL Il.

IIIa, IIIb, IVa e IVb - nas saídas a e b dos flip-flop de rearme III e IV.

Acima de certo valor de ta, tb permanece constante. Quando ta cresce mais pulsos LO de duração tp = ta - tb aparecem no ponto D, como explicamos na conexão correspondente para a monitoração de largura de pulsos (figura 8, linha E, A e D). Para ta = tb e para T2, tb é também constante, e ta > tb.

As saídas B e D são ligadas a dois "flip-flop" de rearmação ("reset") III e IV, um dos quais é retardado. Os dois "flip-flop" são definitivamente armados pelos pulsos em B (figura 8, linhas lia e b; IVa e b, para Ti).

Dependendo da duração do pulso ta, as seguintes das três opções de saída em D são disponíveis:

X, Y - rias saídas X e Y dos elementos exclusive OR V (II la e IVb determina X, e II lb e IVa determina Y). Z', Z, Z :nas saídas Z'. (sem retardo, ou seja, sem o capacitor Cd3) Z com retardo (ou sèja com o capacitor Cd3) e 2 (saída principal).

|| - Sinal H| - (ta = tb, duração T1 na figura 8) os estados dos dois “flip-flop” se mantêm inalterados;

2. Pulso LO de curta duração - (ta > tb, duração T2 e T3 na figura 8); ponto b no "flip-flop" IV é lavado ao nível Hi e o estado do "flip-flop" III permanece inalterado (figura 8, linhas lia e b, IVa e b, para T2 e T3);

3. Um pulso LO de longa duração (ta > tb; duração T4 na figura 8, ambos os "flip-flop" mudam de estado - figura 8, linhas lila e b, IVa e b para T4).

Se a frequência for muito alta ou muito baixa (1/T1 ou 1/1-4 na figura 8) ambos os "flip-flop" têm a mesma forma de informação de saída. Informação diferente aparece somente numa determinada faixa (T2 e T3 na figura 8) que é ajustável por meio do capacitor Cd2.

O nível lógico HI aparece na saída Z de um elemento exclusive OR V quando a informação fornecida pelos "flip-flop" III e IV nos quais é conectado não for idêntica. O ponto a do "flip-flop" III está então no nível LO e o ponto b do "flip-flop" IV estará no nível Hl (figura 8, linhas IIIa e IVb para T2 e T3). Isto resulta em saídas Hl tanto na saída X e Y como na saída Z (figura 8, linhas X, Y e Z).

CAPACITÂNCIA DOS CAPACITORES Cd1, Cd2 e Cd3

O limite superior para a gama de frequências de operação é, como já foi observado, feito peio capacitor Cd1. O diagrama mostrado na figura 9 é usado para determinar a capacitância requerido por Cd1 para certo limite de frequência de corte.

A capacitância Cd2 determina a frequência inferior de corte; Cd2 deve ter uma capacitância aproximadamente de 1/5 de Cd1. De modo a assegurar uma saída estável, é conveniente fixar Cd3 de modo que tenha uma capacitância aproximadamente 3 vezes maior que Cd1.