Na primeira parte deste artigo (MIC104) focalizamos a arquitetura do 80C51, da Philips Components, um microcontrolador de 8 bits especialmente projetado para controles em tempo real. Continuamos nesta segunda parte a falar deste componente, dedicando o espaço disponível ao Set de Instruções, por onde o projetista terá condições de avaliar melhor o que é possível fazer com este componente e os elementos adicionais da família. Como as aplicações práticas devem exigir muito mais informações, sugerimos aos leitores interessados que consultem o Data Book deste componente.

O Set de Instruções do 80C51 é otimizado justamente para aplicações de controle com 8 bits. Ele fornece uma grande variedade de modos de endereçamento rápido para acessar a RAM interna, e com isso facilitar as operações com bytes em estruturas de dados pequenas.

O Set de Instruções prevê ainda um suporte extensivo para variáveis de 1 bit, como tipos de dados separados, o que permite a manipulação direta do bit em sistemas lógicos e de controle que requeiram um processamento booleana.

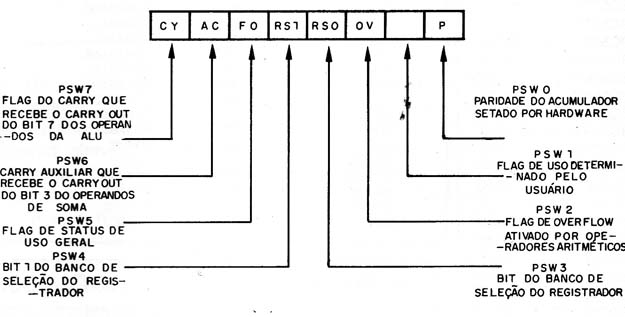

Program Status Word (PSW) O Program Status Word (PSW) contém diversos bits de status que indicam o estado corrente da CPU.

O PSW, mostrado na figura 1, reside no espaço da SFR.

O PSW contém o bit de carry, o carry Auxiliar (para operações em BCD), os dois bancos de registradores para seleção de bits, o aviso de overflow, um bit de paridade e dois bits de uso que pode ser definido pelo usuário.

O bit de carry, além de servir para sua função específica, também serve de acumulador para um certo número de operações booleanas.

O bit de paridade indica o número de "uns" no acumulador. Se P=1 então o acumulador contém um número ímpar de "uns". Se P=0 então o acumulador contém um número par de "uns".

Veja, então, que se levarmos em conta o número de "uns" no acumulador somado ao valor de P teremos sempre um resultado par.

Modos de Endereçamento

Temos os seguintes modos de endereçamentos no 80C51:

a) Modo direto:

Nesta modalidade de endereçamento, o operando é especificado por um endereço de 8 bits na instrução. Somente a RAM interna de dados e a SFR podem ser diretamente endereçadas.

b) Modo indireto:

No endereçamento indireto, a instrução especifica um registrador que contém o endereço do operando. Tanto a RAM interna como a externa podem ser indiretamente endereçadas.

c) Instruções do registrador:

Os bancos de registradores, contendo os registradores de R0 a R7, podem ser acessados por certas instruções que levem uma especificação de registrador de 3 bits juntamente com o código da instrução (opcode).

Instruções que acessam os registradores desta forma são “code efficient', já que se elimina a necessidade de um byte de endereço.

Quando a instrução é executada, um dos oito registradores do banco selecionado é acessado.

Um dos quatro bancos é selecionado no tempo de execução pelos dois bits de seleção de bancos no PSW.

d) Instruções Específicas de Registradores:

Algumas instruções são específicas para certos registradores como, por exemplo, as que sempre operam no Acumulador ou no Data Pointer, de modo que para elas não se necessita de nenhum bit de endereçamento para uso. O opcode faz isso sozinho.

e) Constante imediatas:

O valor de uma constante pode seguir o opcode na Memória de Programa. Por exemplo: MOV A, 100

carrega o acumulador com o número decimal 100.

O mesmo número pode ser especificado em dígitos hexadecimais como 64h.

f) Endereçamento indexado:

Somente a Memória de Programa pode ser acessada com endereçamento indexado, e só é possível, depois, a leitura. Este modo de endereçamento é destinado à leitura de tabelas de consulta na Memória de Programa.

Outro tipo de endereçamento indexado é usado no caso de uma instrução JUMP. Neste caso, o endereçamento de destino de uma instrução JUMP é computado como a soma dos dados do acumulador com o Data Pointer.

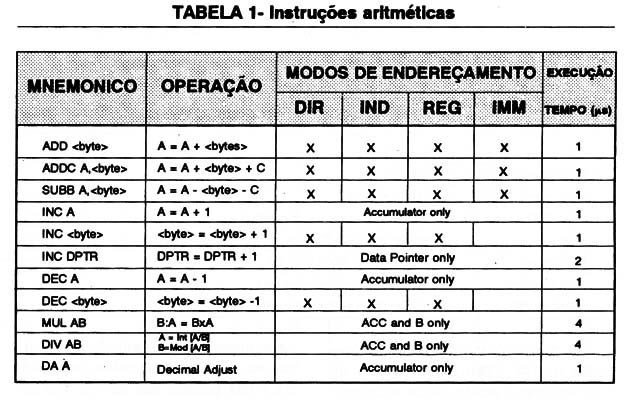

g) Instruções Aritméticas.:

O menu das instruções aritméticas do 80C51 é listado na tabela 1 .

A tabela indica os modos de endereçamento que podem ser usados com cada instrução para acessar o operando. Os tempos de execução listados na tabela 1 são para uma freqüência de clock de 12 MHz. Todas as instruções aritméticas são executadas em 1 us, exceto a lNC DPTR, que leva 2 us, e as instruções de multiplicação e divisão, que levam 4 us.

Note qualquer byte no espaço interno da Memória de Dados pode ser incrementado sem passar pelo Acumulador.

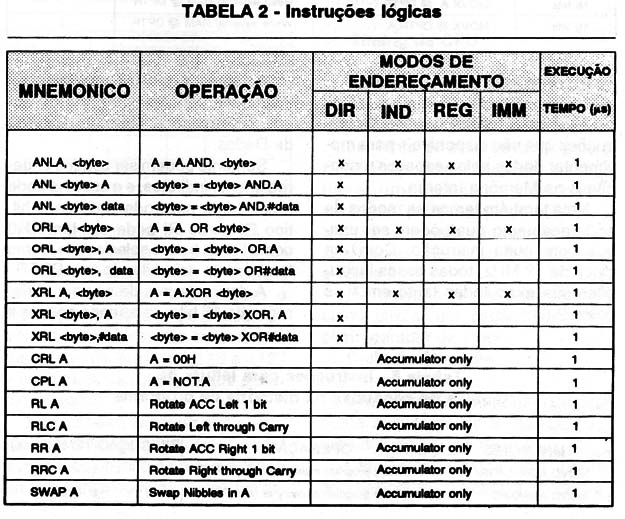

h) Instruções lógicas:

A tabela 2 mostra a lista de instruções lógicas disponíveis no 80C51.

As instruções que realizam operações booleanas (AND, OR, Exclusive OR, NOT) com bytes utilizam bit por bit.

Os modos de endereçamento que podem ser usados para acessar o operando estão listados na mesma tabela.

Todas as instruções lógicas que estejam no acumulador são executadas em 1 us, com base num clock de 12 MHz. As outras demoram 2 us.

Se a operação ocorrer em resposta a uma interrupção, o fato de não se usar o acumulador economiza tempo e esforço no sentido de se introduzir dados na pilha de execução da rotina de serviço.

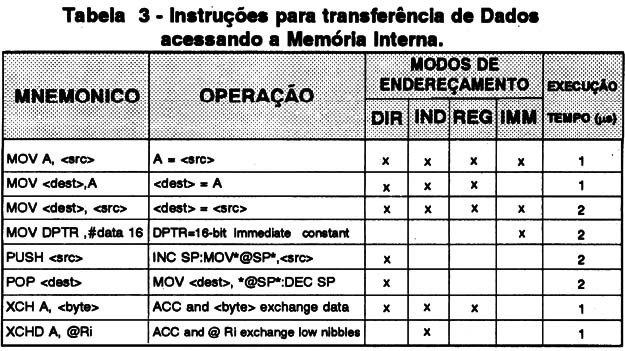

i) Transferidores de dados:

A tabela 3 mostra o menu de instruções que são disponíveis para movimentar dados pelos espaços disponíveis na Memória Interna.

Nela também temos os modos de endereçamento que podem ser usados com cada instrução. Com um clock de 12 MHz, todas essas instruções são executadas tanto em 1 us como 2 us.

A instrução MOV , permite a transferência de dados entre qualquer locação da RAM ou SFR, sem passar pelo acumulador. Lembre-se que até 128 bytes de dados da RAM podem ser acessados somente por endereçamento indireto, e que o espaço da SFR só pode ser acessado por endereçamento direto.

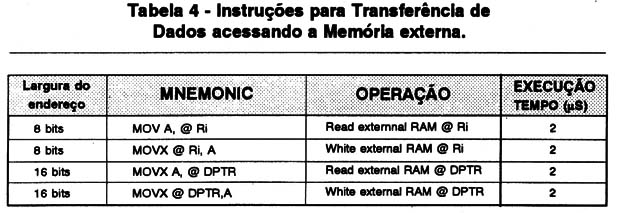

A tabela 4 mostra uma lista de instruções para transferência de dados acessando a Memória Externa de Dados.

Somente podem ser usados endereçamento indiretos, e a escolha pode recair tanto por endereços de 1 bit, tipo Ri, onde Ri pode ser tanto R0 como R1 do banco selecionado, como também de dois bits, do tipo DPTR.

A desvantagem de se usar endereços de 16 bits, se apenas poucos k bytes da RAM externa estão envolvidos num controle, é que os endereços de 16 bits usam todos os 8 bits da port 2 e também o barramento de endereços.

Por outro lado, endereços de 8 bits permitem o endereçamento de poucos bytes da RAM sem sacrificar todo a port 2.

Todas estas instruções são executadas em 2 us corn um clock de 12 MHz.

Observe que em todos os acessos à RAM externa o acumulador está funcionando como destino e origem dos dados.

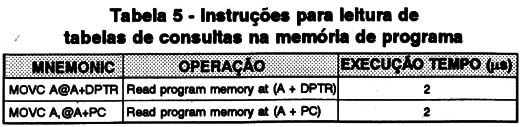

A tabela 5 mostra as duas instruções que são disponíveis para a leitura de tabelas de consultas na Memória de Programa.

Como estas instruções acessam somente a Memória de Programa, as tabelas de consulta somente podem ser consultadas, e não atualizadas.

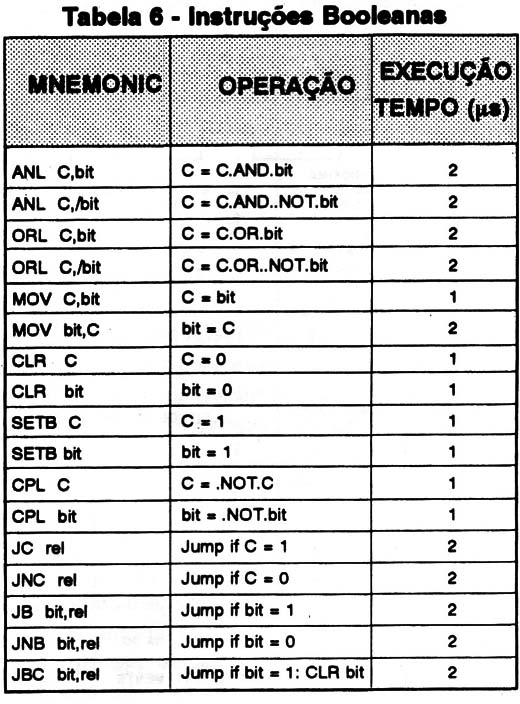

j) Instruções Booleanas:

Os dispositivos 80C51 contém um processador completo para instruções booleanas (bit único).

A RAM interna contém 128 bits endereçáveis, e o espaço SFR pode aceitar até 128 bits endereçáveis.

Todas as Linhas de ports são endereçáveis por bit, e cada um pode ser tratado como uma port de bit único.

As instruções que acessam estes bits não têm uma única função: podem operar segundo um menu completo de opções como deslocamento, fixação, apagamento, complementação, porta OR, AND etc.

Estas operações de bit único não são facilmente obtidas em outras arquiteturas sem a ajuda de uma boa quantidade de software orientado para esta finalidade.

O Set de Instruções para o processador booleano é mostrado na tabela 6.

Os endereços dos bits de 00h até 7FH estão nos 128-inferiores, e os endereços de 80h até FFH estão no espaço SFR.

Note que o Set de instruções booleanas inclui operações ANL e ORL, mas não a operação XRL (Exclusive OR). Uma operação XRL é fácil de implementar por software.

Offset relativo: Os endereços de destino para estes saltos são especificados ao dispositivo por meio de um arquivo ou por um endereço real na Memória de Programa.

k) Instruções de Salto (JUMP):

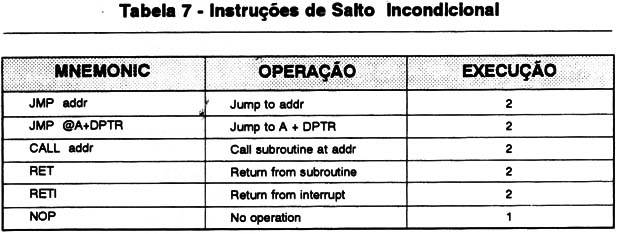

A tabela 7 mostra uma lista de jumps incondicionais com o tempo de execução para um clock de 12 MHz.

A distância do salto está limitada à faixa de -128 a +127 bytes relativos à instrução que segue o JMP. JMP é a forma mnemônica da instrução.

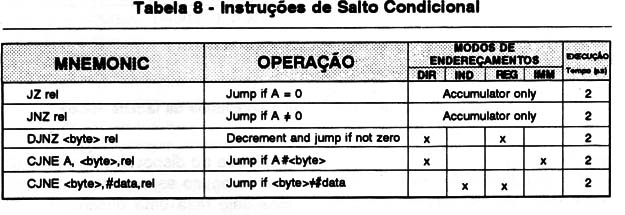

A tabela 8 mostra a lista de jumps condicionais disponíveis no 80C51.

Todos estes jumps especificam o endereço de destino pelo método de offset relativo, e por isso estão limitados a uma distância de -128 a +127 bytes a partir da instrução que determina o salto.

E importante observar que o usuário específica ao assembler o endereço real de destino da mesma forma que em jumps comuns: como um arquivo de constantes de 16 bits.

Uma outra aplicação para esta instrução é nas comparações do tipo “menor que".

Timing da CPU

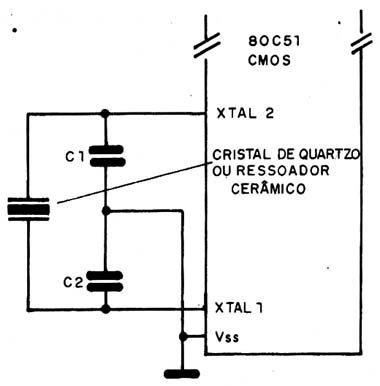

Todos os microcontroladores 80C51 possuem um oscilador on-chip que pode ser usado, se desejado, como fonte de sinal de clock para a CPU. Para usar o oscilador on-chip,

ligue um cristal ou ressonador cerâmico entre os pinos XTAL1 e XTAL2 do microcontrolador e capacitores à terra, conforme mostra a figura 2.

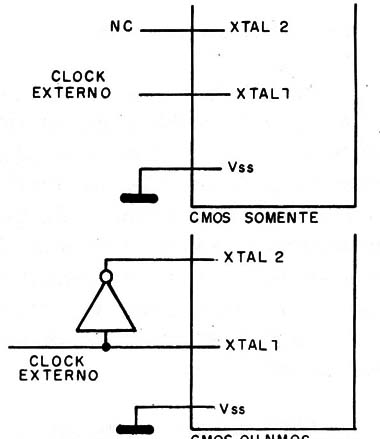

Na figura 3 temos exemplos de como utilizar um oscilador externo como gerador de clock.

Ciclo de Máquina

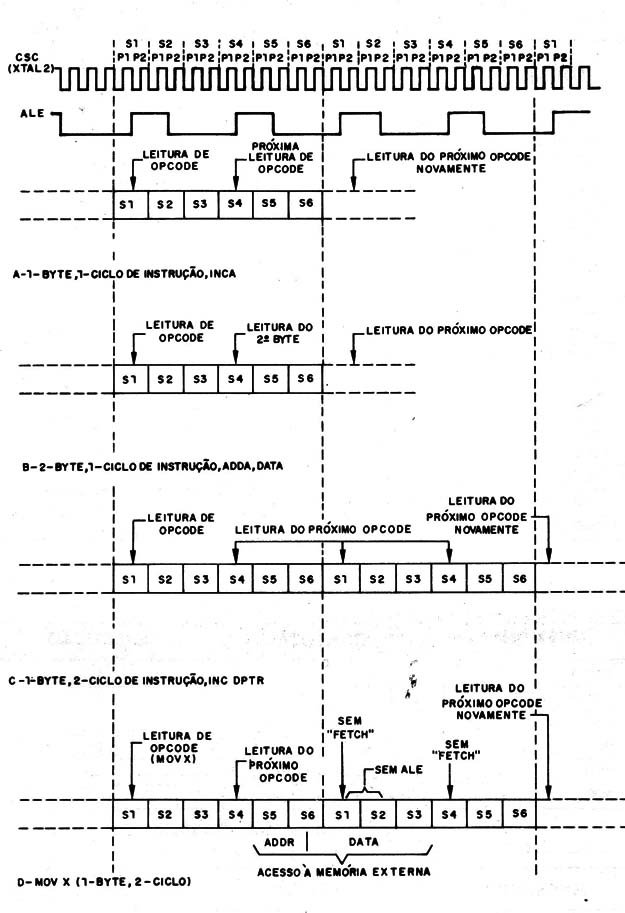

Um ciclo de máquina consiste numa seqüência de 6 estados, numeradas de S1 até S6.

Cada estado exige pelo menos dois períodos do oscilador, o que significa que um ciclo de máquina demora 12 ciclos do oscilador, correspondendo a 1 us se a freqüência do clock for de 12 MHz.

Cada estado é divido em metades que correspondem a Fase 1 e Fase 2.

A figura 4 mostra a seqüência de estados e fases para diversos tipos de instruções.

As seqüências descritas são as mesmas tanto para o caso do uso de uma Memória de Programa interna como externa. O tempo de execução também não depende do fato destas memórias usadas serem internas ou externas.

Estrutura de interrupções

O 80051, em sua versão sem ROM e com EPROM, possuem 5 fontes de interrupções: 2 externas, 2 por timer e a port serial de interrupção.

Damos a seguir uma visão geral da estrutura de interrupções do dispositivo, já que um aprofundamento maior só é possível com uma análise muito mais detalhada do próprio manual do componente.

Habilitação de interrupções

Cada fonte de interrupção pode ser habilitada ou desabilitada individualmente pela colocação ou retirada de um bit na parte da SFR denominada IE (Interrupt Enable).

Este registro contém também um bit de desabilitação global que permite a habilitação ou desabilitação de todas as interrupções ao mesmo tempo.

Prioridades de interrupção:

Cada fonte de interrupção pode ser individualmente programada para apresentar um ou dois níveis de prioridade pela utilização de um bit no SFR denominado IP (Interrupt Priority).

Uma interrupção de baixa prioridade pode ser interrompida por uma interrupção de alta prioridade, mas não por outra de baixa prioridade. Se dois pedidos de interrupção são recebidos ao mesmo tempo, o pedido de maior nível de prioridade é que será atendido.

Se duas instruções de interrupção de mesma prioridade são recebidas ao mesmo tempo, uma seqüência interna de avaliação determina qual deve ser atendida.

Simulando um Terceiro Nível de Prioridade Via Software: Algumas aplicações exigem mais do que os dois níveis de prioridade disponíveis on-chip no 80051.

Nestes casos, um software relativamente simples pode ser usado para ter o mesmo efeito de um terceiro nível de prioridade.

Este software acrescenta um tempo de 10 us (com 12 MHz) para as interrupções de prioridade.

Conclusão

A descrição da arquitetura que demos foi simplificada, já que a complexidade do dispositivo não permite que no pouco espaço de que dispomos seja feita uma descrição completa.

No entanto, acreditamos que ela tenha sido suficiente para permitir ao projetista uma visão das possibilidades do dispositivo.

Na última parte deste artigo, que será publicada na próxima edição, falaremos do hardware da família do 80051, completando assim a abordagem deste poderoso microcontrolador da Philips Components.

Bibliografia: 80051 - based 8-bit Microcontrollers Data Handbook Philips Components – 1991.