Os microcontroladores são utilizados numa enorme gama de aplicações práticas no mundo moderno. Estas aplicações vão desde a instrumentação médica e industrial até aparelhos para o grande consumidor e de uso automotivo. Uma das famílias mais importantes de microcontroladores de 8 bits é a que tem por base o 8051, e modelos derivados apropriados para certas aplicações, como o 8oC51, que é justamente o assunto central deste artigo. Nele focalizaremos as aplicações deste microcontrolador, sua estrutura interna e as funções de que ele dispõe. Mais informações sobre este componente e todos que fazem parte de sua família podem ser obtidas a partir do próprio manual da Philips.

Este artigo é de 1993. O 8051 é apenas utilizado atualmente com finalidade didática e recreativa, pois existem outros microcontroladores mais completos. No entanto, como curiosidade, ou para entender melhor como funcionam outros microcontroladores este artigo é perfeitamente válido.

A família de microcontroladores e periféricos que tem por base o 8051 é baseada totalmente no padrão industrial para 8 bits de alta performance, possuindo uma arquitetura otimizada para aplicações em controle seqüencial em tempo real.

Os componentes desta família encontram aplicações que vão desde o controle de máquinas industriais e de instrumentação até o controle automotivo.

Os dispositivos da série podem ser obtidos em versões com 4ROM ou EPROM internas ou somente com a CPU.

Com exceção do 830751, todos os dispositivos desta família podem endereçar até 64 k bytes tanto de programa como de memória de dados.

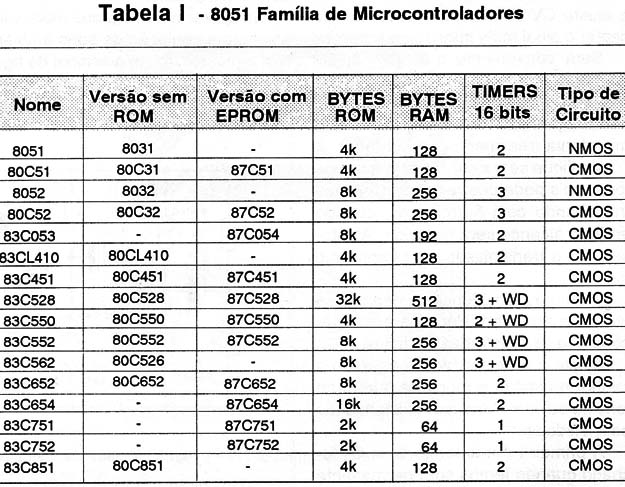

Na tabela l temos os dispositivos que compõem esta família de microcontroladores.

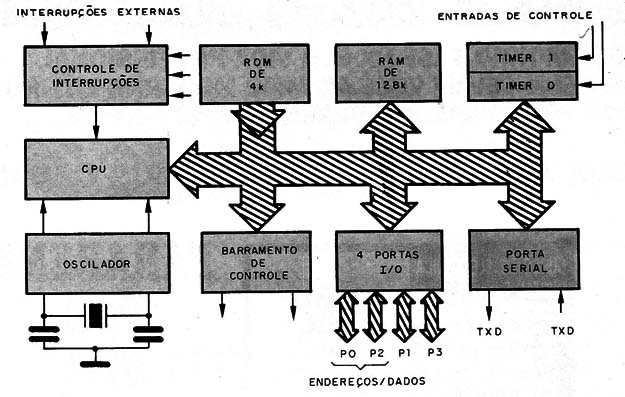

O 8051, que é o elemento básico, contém as seguintes funções:

- CPU de 8 bits otimizada para aplicações em controle;

- Capacidade de processamento BooIeana extensiva (lógica de bit único);

- 32 linhas bidirecionais e individualmente endereçáveis de entrada e saí-

da (I/O);

- RAM de dados de 128 bytes on-chip;

- Dois temporizadores/contadores de 16 bits;

- µART duplex completa;

- 5 entradas de interrupções com dois níveis de prioridade;

- Oscilador de clock on-chip;

-Mem. de prog. de 4 k bytes on-chip;

- Espaço para endereçamento de programa na memória de 64 k bytes;

- Espaço para endereçamento da memória de dados de 64 k bytes;

- Disponível tanto em invólucro DIL de 40 pinos como invólucro PLC de 44 pinos.

O microcontrolador 80C51 é a versão CMOS do 8051, sendo totalmente compatível com o 8051 em termos funcionais.

No entanto, como se trata de dispositivo CMOS (diferentemente do 8051, que é NMOS) o consumo é muito menor.

Na figura 1 temos o diagrama em blocos do 80C51, a partir do qual faremos sua análise.

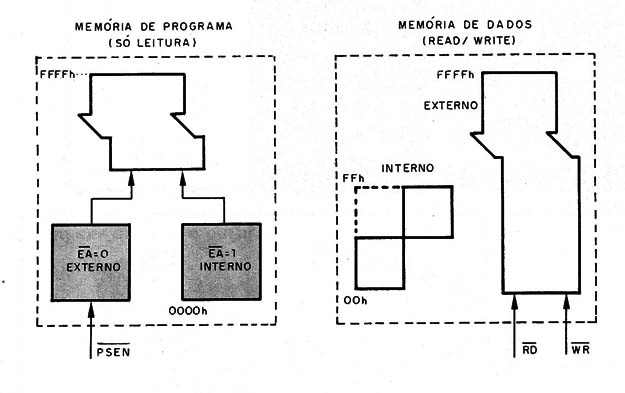

Todos os membros desta série possuem espaços separados para endereços e programas de dados, conforme mostra o diagrama da estrutura da memória na figura 2.

Esta separação permite que os dados da memória sejam acessados por um endereçamento de 8 bits, o que resulta numa armazenagem e manipulação mais rápida quando feito por uma CPU de 8 bits.

Entretanto, endereços de 16 bits também podem ser usados, gerados pelo registrador DPTR.

A Memória de programa (ROM ou EPROM) pode apenas ser lida e não gravada. Temos disponíveis 64 k bytes de espaço para a Memória de Programa.

No 80C51, os 4 k bytes inferiores estão on-chip. Nas versões sem ROM, toda a Memória de Programa é externa. O strobe para a leitura da memória é o PSEN (Program Store Enab/e).

A Memória de Dados (RAM) ocupa um espaço separado de endereçamento a partir do Programa de Memória. No 80C51, os 128 bytes da Memória de Dados estão on-chip.

Até 64 k bytes de uma RAM externa podem ser endereçados pelo espaço da Memória de Dados externa.

Na versão sem ROM, os 128 bytes inferiores são on-chip.

A CPU gera os sinais de leitura e gravação (RD e WR), conforme necessário, durante os acessos à memória externa.

Memórias de Dados externas podem ser combinadas com Memórias de Programas, se desejado, através da aplicação de sinais RD e PSEN nas entradas de uma porta AND e utilizando-se a saída desta porta como strobe de leitura para a memória de Dados/Programa externa.

Memória de Programa

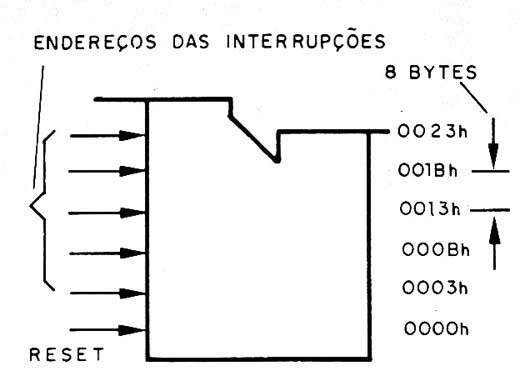

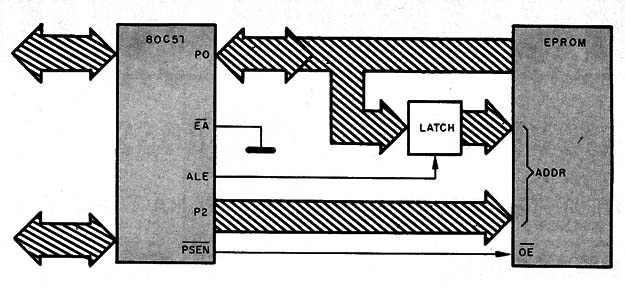

Na figura 3 temos o diagrama em blocos da Memória de Programa.

Como mostrado na figura 3, cada interrupção é designada por um endereço fixo na Memória de Programa.

A interrupção faz com que a CPU salte para o endereço correspondente, onde tem início então a rotina de serviço (rotina de tratamento de interrupção)

Uma interrupção 0 externa, por exemplo, determina o endereço 0003h.

Se uma interrupção O externa for usada, a rotina de serviço deve começar pelo endereço 0003h. Se a interrupção não for usada, o endereço estará disponível como Memória de Programa de uso geral.

Os endereços das sub-rotinas de tratamento de interrupção estão separados por intervalos de 8 bytes: 0003h para interrupção externa 0, 000Bh para o timer 0, 0003h para a interrupção externa 1, 000Bh para o timer, etc.

Se uma rotina de tratamento de interrupção for suficientemente curta (como no caso de aplicações em controle), ela pode ficar totalmente no intervalo disponível de 8 bytes.

Rotinas de serviço mais longas podem usar uma instrução de salto para evitar endereços de interrupções subseqüentes, se outras interrupções não estiverem em uso. Os 4 k bytes inferiores da Memória de Programa podem estar tanto na ROM on-chip como numa ROM externa.

O pino EA (External Access) permite fazer a seleção.

No 80C51, se o pino EA for ligado ao Vcc então o programa vai buscar os endereços de 0000h até 0FFFh na ROM interna, e de 10000h até FFFFh na ROM externa;

Se o pino EA for ligado ao Vss, então o programa trabalha com os endereços da ROM externa. O hardware para a execução de programas externos é mostrado na figura 4.

Observe que as 16 linhas de l/O (ports 0 e 2) são dedicadas ao barramento de instruções durante as ações externas da Memória de Programa.

A port 0 (PO, na figura 4) serve como barramento multiplexado de endereços e dados.

Ela emite o byte inferior do Contador de Programa (PCL) como um endereço e então vai a um estado flutuante, esperando a chegada do byte de código da Memória de Programa.

Durante o intervalo de tempo em que o byte inferior do Contador de Programa for válido na port 0, o sinal ALE (Address Latch Enable) joga este byte num latch de endereçamento.

Enquanto isso, a port 2 (P2, na figura 4) emite um byte superior do Contador de Programa (PCH). Então, PSEN, através do strobe, permite que o microcontrolador leia o byte de código na EPROM. Os endereços da Memória de Programa são sempre de 16 bits, mesmo quando se usa um espaço real de menos de 64 bytes.

A execução do programa externo, nestas condições, sacrifica então duas ports de 8 bits, P0 e P2, para funcionar no endereçamento da Memória de Programa.

A metade direita da figura 2 mostra os espaços internos e externos da Memória de Dados disponível no 80C51.

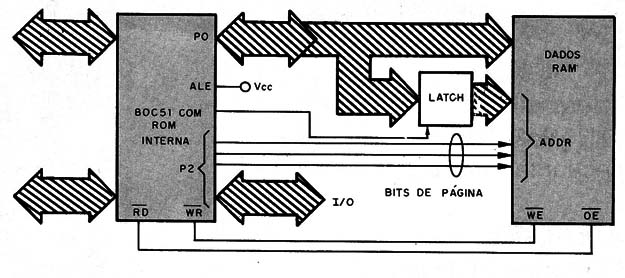

Na figura 5 temos uma configuração de hardware que permite acessar até 2 k bytes de uma memória RAM externa. Neste caso, a CPU opera a partir da ROM interna.

A port 0 serve como um acesso multiplexado de endereços e dados para a RAM, e 3 linhas da port 2 são usadas para paginar a RAM;

A CPU gera os sinais RD e WR à medida que necessários, durante o acesso à RAM externa.

Pode-se usar até 64 k bytes de memória externa.

Os endereços para acessar os dados da memória externa podem usar tanto 1 como 2 bytes de extensão.

Os endereços de 1 byte também são usados em conjunto com uma ou mais linhas de I/O para paginar a RAM, conforme mostra a mesma figura 5.

Endereços de dois bytes também podem ser usados, caso em que a parte mais alta é emitida pela port 2.

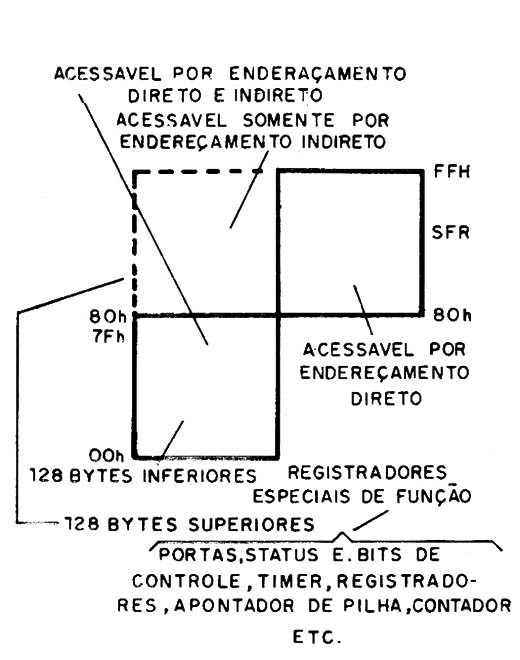

A memória interna de dados é mapeada conforme mostra a figura 6.

O espaço da memória é dividido em três blocos que são referidos como: 128-inferiores, 128-superiores e espaço do SFH. (Special Function Register).

Os endereços da Memória de Dados internos são sempre de um byte de extensão, o que implica num espaço para endereços somente de 256 bytes.

Além disso, os modos de endereçamento da RAM interna podem de fato acomodar 384 bytes utilizando um truque simples: os endereços diretos acima de 7Fh acessam um espaço da memória e os endereços superiores a 7Fh acessam um espaço diferente.

A figura 6 mostra os 128-superiores e o SFR sendo ocupados pelo mesmo bloco de endereços: de 80h até ffh, enquanto que na realidade eles são entidades fisicamente diferentes.

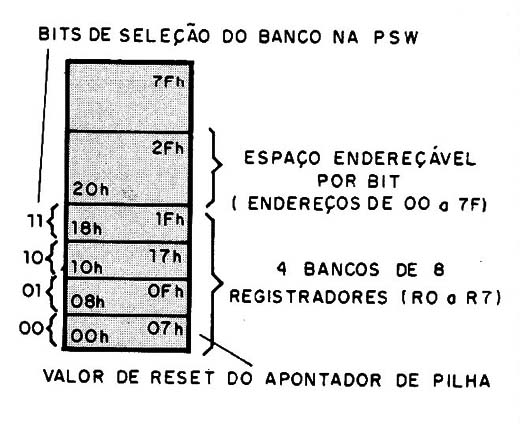

Os 128 bytes inferiores da RAM estão presentes em todos os dispositivos 80C51, como mapeado na figura 7.

Os 32 bytes inferiores são agrupa- dos em 4 bancos de 8 registradores.

As instruções do programa chamam estes registradores externamente de RO a R7. Dois bits do PSW (Program Status Wora) selecionam qual o banco de registrador que vai ser usado.

Este procedimento permite uma utilização mais eficiente do espaço para código, já que as instruções são mais curtas do que as que usam endereçamento direto.

Os 16 bytes seguintes, acima dos bancos de registradores, formam um bloco de espaço de memória endereçável por bit.

O set de instruções do 80C51 inclui uma ampla seleção de instruções de bit único, e os 128 bits desta área podem ser diretamente endereçados por estas instruções, Os endereços de bits nesta área vão de 00h a 7Fh. Todos os bytes nos 128-inferiores podem ser acessados tanto por endereçamento indireto como direto.

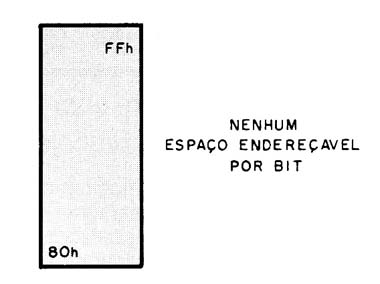

Os 128-superiores, conforme mostra a figura 8, podem ser acessados apenas por endereçamento indireto.

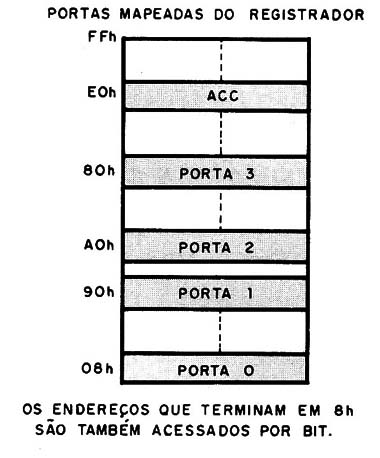

Na figura 9 temos uma visão do Special Function Register (SFR) e o espaço que ele ocupa.

Esta estrutura inclui latches de portas, timers, controles periféricos etc. Estes registradores podem ser acessados somente por endereçamento direto.

Dezesseis endereços no espaço SFFl são acessados tanto por byte como por bit. Os SCF acessados por bit são os que têm endereços terminados em 0h ou 8h.

No próximo artigo (MIC105) continuaremos a falar do 80C51, abordando os recursos do Instruction Set desta família.

Através desta segunda parte do artigo os projetistas poderão ter uma visão melhor de como e onde usar o microcontrolador 80C51 e seus periféricos. Os dados deste artigo foram obtidos do “8051-Based 8-bit Microcontrollers Data Handbook”, da Philips Components de 1991.