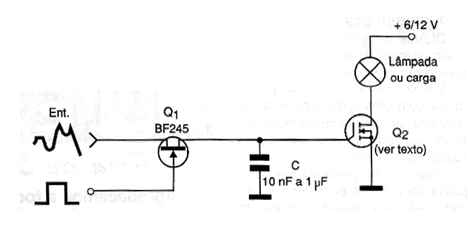

A altíssima resistência de entrada de um Power-FET possibilita a elaboração de um circuito de amostragem e retenção para sinais analógicos, bastante simples. Na figura temos o circuito básico para esta aplicação que funciona da seguinte maneira. Quando o FET de junção (Q1) é habilitado o sinal a ser amostrado carrega o capacitor C com a tensão que ele apresenta naquele instante. Uma vez desabilitado, a tensão no capacitor pode ser mantida por um bom tempo até a amostragem seguinte. Esta tensão amostrada que está no capacitor determina a condução do transistor de efeito de campo de potência e, portanto, a corrente na carga.